摘要:分析表明,新能源以及無人駕駛汽車的迅速發展,車規芯片的作用愈加重要,這是芯片產業應用的一重要方向。闡述集成電路設計公司進入車規芯片領域的相關驗證流程及規范標準,車規芯片的相關可靠性驗證以及失效分析,探討了車規芯片量產化的零缺陷目標,分析國內車規芯片發展中存在的問題 與其局限性,展望發展方向。 0 引言 隨著汽車電子的深入發展,以及汽車行業確立的新四化(電動化、網聯化、智能化、共享化)發展方向,這給半導體芯片在汽車領域的應用帶來新的機遇。近年的需求更是飛速發展,這給汽車市場帶來新的產業變革。使得車規芯片在電源控制、底盤控制和信息娛樂等應用領域扮演著越來越重要的角色[1]。過去5年的時間全球汽車半導體市場年復合增長率約為4.8%,而中國汽車半導體市場規模復合增速更是達到11.6%。這主要是因為新能源汽車電子化程度越來越高,帶來各類汽車半導體需求的大幅上漲[2]。據德勤預測,汽車半導體收入將在2022年突破600億美元[3],勢必會吸引更多芯片廠商參與其中。 相比消費類電子芯片,車規芯片要求更加苛刻,(1)車規芯片是高于消費類以及工業芯片標準;(2)車規芯片對工作環境有更嚴苛的要求,如,溫度,濕度,EMC以及有害氣體侵蝕等方面,根據其不同的應用有不同的需求;(3)車規芯片開發驗證花費多,門檻高,周期長;(4)需要通過相應的審核標準。 車規芯片有兩個條件,(1)符合零失效的供應鏈質量管理標準IATF 16949規范;(2)滿足由北美汽車產業所推的AEC可靠性標準。由于車規芯片較長的設計周期和較高的技術壁壘,整個汽車芯片行業呈現國外巨頭壟斷的格局,如英飛凌,瑞薩等專注于高端車規芯片的細分市場。同時國內亦涌現出了幾十家芯片設計公司成為汽車電子芯片的供應商,類型范圍涵蓋輔助駕駛、中控、電池管理、圖像傳感器和信號處理器等[4]。 國際傳統車企如豐田、福特和大眾等更是積極投身汽車電子芯片的研發中,國內一些主流車廠也加入芯片的研發當中,像比亞迪、上汽等以各種形式參與芯片研發,擁抱汽車芯片產業的新革命,他們更容易結合自身應用場景以及財力來推動芯片設計的快速導入。以新能源為代表的特斯拉更是推出FSD芯片,一場圍繞高級別自動駕駛的競爭也已經開始,汽車行業加速進入智能化時代。 本文結合車規芯片的巨大市場,根據其應用特點以及進入該領域的標準要求,重點會對進入該領域的驗證條件IATF 16949規范和AEC可靠性標準進行探討,通過老化篩選測試及失效芯片的根因分析,確保車規芯片的可靠性以實現零失效的目標。最后圍繞車規芯片驗證規范的標準化,可靠性驗證的全面化,高效的老化篩選測試以及專業的失效分析進行展望。

1 車規芯片的相關驗證

1.1 IATF16949 在汽車行業,質量認證活動在世界各個地區均有自己的行業認證標準和要求,例如汽車制造強國德國汽車工業的 VDA6.1標準、法國的EAQF標準、意大利的AVSQ標準以及美國的QS-9000標準。成立于1997年的國際汽車特別工作組(IATF)為實現汽車行業統一的全球質量體系標準和認證,與國際標準化組織(ISO/TC 176)合作,以各國汽車工業標準為基礎,并于1999年制定并推出質量要求ISO/TS16949技術規范,《IATF16949》是當前的[敏感詞]版質量管理體系標準[5]。IATF16949是國際汽車小組是以顧客為導向同時兼顧其特殊要求,針對近年汽車行業比較關注的一些問題,如汽車安全等,在標準中增加了新的條款[6,7]。IATF16949規范適用于汽車制造廠和其直接的零部件供應商,這些廠家直接與汽車生產有關,可以加工制造活動,并通過這種活動使的產品得以增值。例如在芯片整個產業鏈中,晶圓制造廠、封裝廠等需要嚴格按照IATF16949標準開展汽車芯片的制造。而那些只具備支持功能的單位,如設計和配送中心等,不需要獲得該認證[8]。

1.2 AEC標準認證 汽 車 電 子 委 員 會 ( A E C : A u t o m o t i v e Electronics Council)由三大北美汽車公司(克萊斯勒、福特和通用汽車)在1994年為建立一套通用的質量系統標準而設立[9]。AEC建立了產品質量控制的標準,推動了汽車零部件通用性的實施,同時為市場的快速發展打下良好的基礎。其規范標準主要包括AEC-Q100(集成電路IC)、AEC-Q101(離散組件)、AEC-Q102(離散光電LED)、AEC-Q104(多芯片組件)、AEC-Q200(被動組件)。其中AEC-Q100是專門針對IC集成電路的驗證規范,其目的是要確定器件在應用中能夠通過應力測試達到某種要求的品質和可靠度[10]。

1.2.1車規芯片設計 從產品的使用功能,工作條件(電壓、頻率范圍等),以及芯片所用的單元設計庫技術等方面進行驗證,確定電路設計原則,滿足車規芯片要求。執行的過程可以識別潛在的故障模式及對系統和客戶的影響,確定其嚴重程度以及可能的原因。考慮冗余設計,該設計可以通過糾錯碼的形式避免潛在的數據保留錯誤,替換有缺陷的單元。建立自我檢測機制,通過芯片合理的測試時間,在電路中增加一些路徑節點進行測試,及時發現有問題單元,并進行相關的處理,降低因為工藝波動帶來的影響。 在芯片設計階段,就要開始著手芯片可靠性實驗的考量,使用計算機輔助工程分析和仿真工具可以更短的時間內提高產品可靠性。有限元分析,熱分析以及可靠性預測模型等工具正在得到越來越廣泛的應用,這樣車規芯片在設計之初主動來提高器件可靠性和穩定性。

1.2.2 芯片晶圓制造 晶圓制造主要步驟有離子注入,光刻,蝕刻和鍍膜等工藝流程。在每一道工序中,均需要通過數學統計研究分析工具,找出最優參數,以達到提高芯片良率和品質的要求。fab廠通過檢測每道工序具體測試參數,芯片數量,頻率等信息,可以保證制程的穩定性。

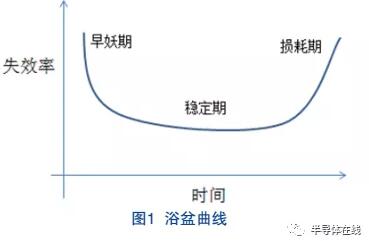

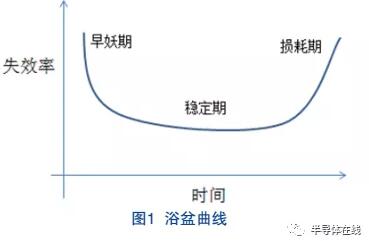

1.2.3 芯片測試 在合理的時間內盡可能實現[敏感詞]的測試覆蓋率提前篩選出不良品,避免流到客戶端。芯片測試更快更有效的一種重要方式是通過芯片的自測設計來實現,也可以減少對外部ATE資源的依賴。良品測試limit標準設定可以采用AEC_Q004文檔中的建議,基于一定的數據量標準差公式來設定,Static PAT Limits=Robust Mean±6 Robust Sigma。通過大數據分析,管控工藝波動,保證產品質量穩定性,該方法可以定期進行Review和更新。產品使用之前的失效為良率,產品使用過程中的失效為可靠性,因此芯片的測試直接關系到芯片的可靠性。 浴盆曲線是由三部分組成,早妖期、穩定期和損耗期。老化篩選測試(Burn in)是ATV(Automotive)芯片測試很重要的一個步驟,其主要作用是在芯片出貨前去除產品的早期失效芯片實現用戶端的高可靠性。早妖期是失效率相對較高的階段,芯片失效原因通常是因為芯片天生的缺陷或問題所導致,如設計缺陷,工藝制造異常或材料固有的缺陷等。這些缺陷會引發與時間、應力相關的故障,其故障率通常按Dppm進行表征。具體方法是先對芯片進行一定時間的100%老化測試,例如加偏壓,加高溫等,然后再進行正常的ATE 測試進行篩選[11]。浴盆曲線(圖1)中的穩定期代表著芯片在使用壽命期間失效率是相對穩定的,通常按FIT(failure in time)或MTBF(Mean Time Between Failure)小時數來描述其失效。損耗階段表明芯片的失效率開始因為芯片內在電路損耗而上升,代表已到達了芯片的極限使用壽命。

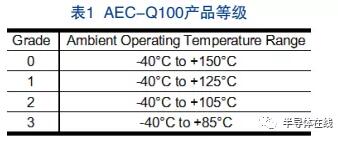

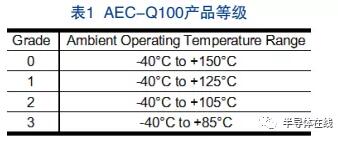

1.2.4 AEC-Q100芯片可靠性驗證 AEC-Q100作為汽車電子可靠性驗證的標準,其主要目的:(1)客戶有可以參考的標準規范;(2)芯片供貨商可以排除芯片可能存在的潛在故障。表1是AEC-Q100根據器件工作環境溫度分為不同的產品等級,這與芯片具體應用有關,其中最嚴格[敏感詞]等級標準的工作溫度范圍是-40~150℃之間。芯片供應商需要不斷的持續優化產品設計,采用先進穩定的制造以及封裝工藝,同時采用嚴格的測試程序篩選達到車規芯片對工作溫度和可靠度的高標準要求。

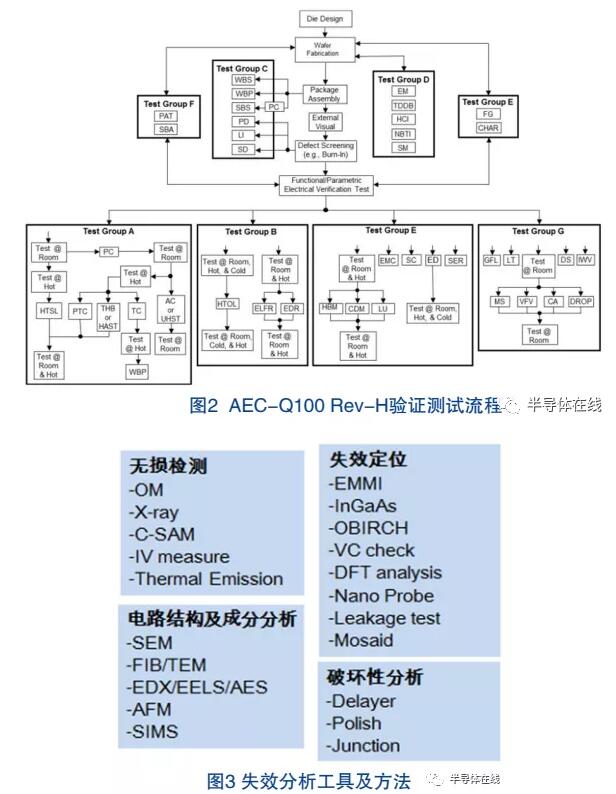

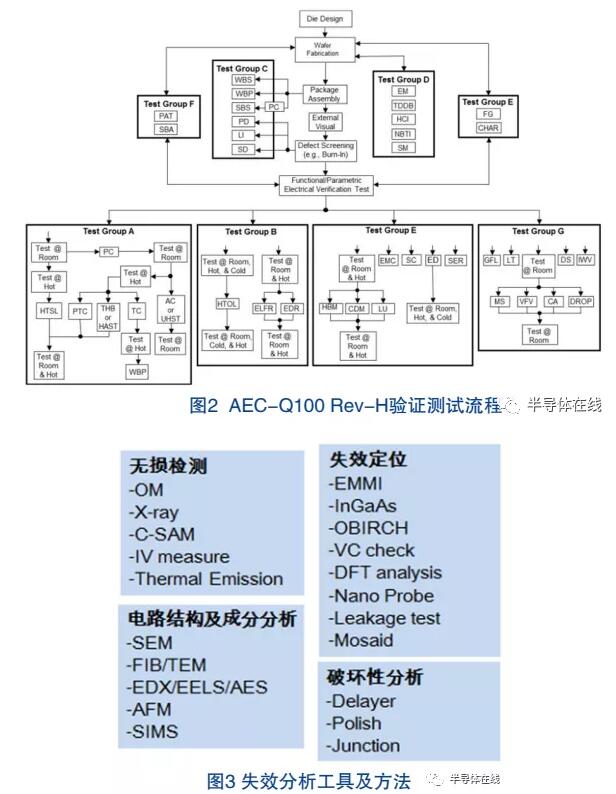

AEC-Q100明確了芯片在設計,制造,封裝,測試和量產等各個階段所需要的驗證以及相關的卡控標準。從其內容來看,具體包含7大類別共41項的測試,如圖2所示即為AEC-Q100 Rev-H 的驗證流程及規范內容[12]。大致分為:Group A(加速環境應力測試)、Group B(加速工作壽命測試)、Group C(封裝完整性測試)、Group D(晶圓級可靠性測試)、Group E(電性驗證測試)、Group F (可篩選性測試)、Group G(密封型封裝完整性測試)。 目前AEC-Q100已成為車規芯片的重要規范,通常車規芯片供應商需要完成其項目的驗證,然后以“自我宣告”的方式說明其產品通過了其相關的驗證結果,AEC不會給予供應商任何認證。因為樣本數量少,這些測試是必要不充分測試,反映此方法的局限性。測試項目可以用于否定器件的可用性,但不能確定大批量量產芯片在具體場景下均滿足使用標準。所以量產車規芯片的老化篩選測試顯得尤為重要,使得提供給客戶的芯片處于穩定期,提高了車規芯片的可靠度。同時通過失效分析,一方面可以識別造成該芯片失效的根因,采取相應措施根除該問題,另一方面針對固有缺陷的問題,可以優化以及加嚴測試進行篩除,從而實現車規芯片零失效率的目標。

2 失效 半導體在研制、生產和使用過程中失效是不可避免發生的。通過有針對性的失效分析:(1)可以協助設計人員找出芯片設計上的缺陷,例如通過FIB電路修補的方式亦可驗證該結果。(2)可以找出芯片在制造,封裝等工藝中存在的缺陷,提出切實可行的改善方案。(3)評估不同測試向量的有效性,為生產測試提供必要的補充。芯片的失效分析主要是立足于微觀世界,從電性、物理,化學和材料的角度對其進行觀察和分析,從本質上找出造成芯片失效的原因[13],其主要分析工具和試驗方法如圖3所示。 半導體芯片工藝制程復雜度越來越高,這也為失效分析帶來更多的難度,例如線寬的減小對電鏡的分辨率要求更高,金屬層間距的減小對樣品制備增加了難度等。通過失效現象,同時結合芯片設計以及工作原理,掌握準確的芯片信息資料與數據,才能進行正確的分析和判斷。一般半導體芯片使用后的失效機理可分為以下幾類[14]。 (1)芯片設計存在缺陷,主要體現芯片功能不能實現。 (2)本體類的相關失效,如半導體材料缺陷或封裝中所用基板本身存在的問題。 (3)工藝波動造成的失效。①芯片介質層相關失效,如柵氧,金屬間介質層等缺陷;②硅襯底和SiO2界面間存在缺陷,如Dislocation等;③芯片后端金屬互聯層由于金屬的電遷移或含鹵素及鹵化物的污染造成的金屬腐蝕等;④封裝工藝參數不合理導致的管腳連線造成的短路或者開路等。 (4)測試引入的失效,主要是測試向量電壓設置不合理等造成芯片的Overkill。

3 分析 車規芯片的安全性和可靠性是其首要考慮因素,這不僅反應在芯片設計和開發階段,在測試篩選以及可靠性的驗證也尤為重要。其廣闊的市場前景,使得更多芯片供應商開始進入此領域,加入車規芯片的產業規劃。結合供應鏈質量管理標準IATF16949規范以及AEC-Q100可靠性的要求,當前車規芯片驗證的流程和體系需要更加完善。 (1)車規芯片標準化系統的建立,應由技術專家(汽車整機,芯片設計、制造,封裝以及芯片測試等領域)來建立一套更加專業化,規范化,流程化的標準是必要的。 (2)芯片可靠性驗證需更加全面,產品的可靠性是需要考慮設計進去以及制造出來。 (3)老化測試需更加高效,車規芯片采用100%老化的方法可去除早期失效器件,對于服從威布爾Weibull分布參數β小于1,即早期故障率呈現明顯下降趨勢的情況,會凸顯老化測試的作用。在達到消除芯片早期失效這一目的前提下,老化測試時間越短越好; (4)針對失效芯片根因的分析需要形成閉環。特別需要找出因為工藝制造參數卡控不合理或者測試覆蓋不夠全面而漏掉的失效芯片,因為可能會帶來批次性的問題。不同的失效案例需要從芯片設計、工藝制造、封裝測試、器件使用等角度進行數據收集和綜合分析,找出失效根因進而反饋形成解決方案。同時芯片制造產線需要應用更多主動的專業監控技術,例如,CPK技術、SPC技術和PPM技術,可以對生產能力、工藝穩定性進行分析和預測[15]。

4 結語

在實際的工作中,經常會遇到TSP數據準備以及TSP數據可視化問題,本文利用實際工作經驗,總結出上述兩種制作TSP數據可視化的兩種方法,以解決TSP數據處理問題。

免責聲明:本文轉載自“半導體在線”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室