服務熱線

0755-83044319

發布時間:2024-05-08作者來源:薩科微瀏覽:998

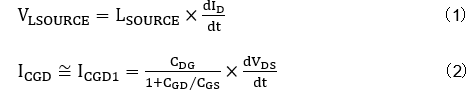

當SiC MOSFET的LS導通時,首先ID會發生變化(見波形示意圖T1)。在這個過程中,LS的ID沿增加方向流動,而HS的ID沿減少方向流動,受到等效電路圖中表示的事件(I)的影響,產生了公式(1)中所示的電動勢。這個電動勢會導致電流流向源極側對CGS進行充電,在LS處將VGS向下推,在HS處將VGS向負極側拉,產生負浪涌(VGS的波形示意圖T1)。

當ID的變化結束時,LS的VDS的電位降低(波形示意圖T2)。因此,公式(2)中的電流會像等效電路圖中的(II)-1、(II)-2那樣流動,并且VGS會分別引發公式(3)、(4)中的電壓上升。

VDS剛剛開始變化后,公式(3)中的VGS上升為主,隨著時間的推移,公式(4)中的VGS也開始上升。換句話說,MOSFET的CGD/CGS比、驅動電路的RG_EXT、柵極驅動信號圖形布線的電感值LTRACE對此具有很大影響。

如等效電路圖所示,HS中的(II)-2的電流ICGD2處于VGS提升方向。因此,本來應該處于OFF狀態的HS因VGS的提升而開始了導通工作。這種現象稱為“誤啟動”。當HS發生誤啟動時,就會與LS的導通工作重疊,致使HS和LS的MOSFET同時導通,從而引發直通電流。

ICGD2會持續流動到LS的導通工作結束,并被積蓄在LTRACE中,但會在VSW變化結束的時間點消失,LTRACE產生電動勢。這就是事件(III)。受RG_EXT等開關條件影響,ICGD2可能會達到幾安培,并且該電動勢可能會增加。

受上述事件(I)、(II)、(III)的影響,LS導通后的Gate-Source電壓呈現出波形示意圖中所示的動作。波形示意圖和等效電路圖的相同編號表示同一事件。另外,圖中VGS的虛線波形表示理想的波形。

外置柵極電阻的影響

下面是SiC MOSFET橋式結構的LS導通時的雙脈沖測試結果。(a)波形圖的外置柵極電阻RG_EXT為0Ω,(b)為10Ω。圖中的(I)、(II)、(III)同前面相應編號的事件。

比較(a)和(b)的波形可以看出,RG_EXT越小,由事件(I)引起的VGS下降就越大。此外,由于開關速度非常快,因此事件(III)在(a)中很突出;但由于RG_EXT為0Ω,因此幾乎沒有觀察到事件(II)的波形。另一方面,在(b)中,事件(II)-2和RG_EXT引起的VGS升程明顯。

從該結果可以清楚地看出,要想降低誘發LS導通時HS誤啟動的事件(II)-2的VGS升程,就需要減小HS關斷時的外置柵極電阻RG_EXT。然而,多數情況下,HS和LS的RG_EXT是相同的,因此,當減小RG_EXT時,LS的dVDS/dt將增加,如公式(1)所示,HS的ICGD會增加。從公式(4)可以看出,結果會導致HS浪涌升高。

有一種對策方法是,使導通時和關斷時的RG_EXT分離,并且僅減小關斷時的RG_EXT。常規方法是使用二極管的方法,如右圖所示。使用這種方法,在導通狀態下工作的電阻只有RG_ON,而在關斷狀態下,二極管導通并成為RG_ON和RG_OFF的并聯電阻。因此,相對于導通時的電阻值,關斷時的電阻值變小。

另外,與最前面說明中使用的波形示意圖不同,HS的VGS波形之所以在緊靠事件(I)之前的位置向正極側振蕩,是因為事件(I)的電流開始流動的瞬間LSOURCE引起的電動勢在通過CGS后立即被觀測到了。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1