服務(wù)熱線

0755-83044319

發(fā)布時間:2024-10-31作者來源:薩科微瀏覽:809

我們可以將集成電路版圖設(shè)計比作城市規(guī)劃和建筑設(shè)計的結(jié)合。就像在有限的土地上規(guī)劃建筑和道路布局一樣,版圖設(shè)計需要在有限的芯片空間上安排晶體管、布線和各類元件,以實現(xiàn)功能和性能的[敏感詞]化。

一、什么是版圖設(shè)計?

版圖設(shè)計是將電路的邏輯功能通過物理層次實現(xiàn)出來的過程。它類似于建筑圖紙的設(shè)計工作,需要通過EDA工具(電子設(shè)計自動化工具)定義各工藝層的形狀、尺寸以及位置。不同層次的工藝圖形(如多晶硅層、金屬層)相互疊加,通過排列和布線形成一個完整的集成電路結(jié)構(gòu)。版圖設(shè)計的核心工作內(nèi)容主要包括布局、布線和尺寸確定。

布局(Placement):這是設(shè)計的[敏感詞]步,類似于把建筑物和公園等設(shè)施在城市地圖上標注位置。版圖設(shè)計中的布局是將晶體管、基本單元(例如門電路)、復雜單元(例如存儲單元等)合理地放置在芯片上。這一步不僅決定了電路的空間結(jié)構(gòu),還直接影響電路的整體性能。

布線(Routing):布線是將布局中各個元件間的連接建立起來的過程,類似于城市中街道的規(guī)劃。在版圖設(shè)計中,布線的合理性將直接影響到電路信號的傳輸速度和整體的可靠性。布線過程需要考慮路徑的長度、繞線的復雜性、信號延時等因素。

尺寸確定(Sizing):尺寸確定涉及確定晶體管的寬度(W)和長度(L)、互連線的寬度以及晶體管與互連線之間的相對尺寸。這相當于在城市規(guī)劃中確定建筑的高度和寬度,以確保整體協(xié)調(diào)和高效。

二、版圖設(shè)計的目標

版圖設(shè)計的核心目標是在滿足電路功能的前提下,[敏感詞]化電路性能,并確保質(zhì)量要求。主要的設(shè)計目標包括以下幾點:

電路功能的實現(xiàn):電路的每個部分都必須在設(shè)計中能夠正常運行。工程師需要確保元件之間的正確連接,并嚴格遵循設(shè)計規(guī)則。

性能的提升:版圖設(shè)計直接關(guān)系到芯片的速度和功耗。合理的布局和布線可以縮短連線長度,從而降低信號延時,提高電路速度。

面積的最小化:集成電路的面積決定了芯片的成本。工程師通過優(yōu)化布局和尺寸設(shè)計,盡量節(jié)省空間,提高集成度,從而降低生產(chǎn)成本。

可靠性和可制造性:確保版圖設(shè)計符合制造工藝要求,并通過設(shè)計規(guī)則檢驗(DRC)、電氣規(guī)則檢驗(ERC)和一致性檢驗(LVS),以保證芯片可以成功生產(chǎn)并長期穩(wěn)定工作。

三、EDA工具的作用

在實際工作中,EDA工具是工程師的得力助手,它幫助設(shè)計人員完成布局、布線以及規(guī)則檢驗等復雜任務(wù)。EDA工具的作用包括:

版圖編輯(Layout Editor):工程師通過布局編輯器定義各個工藝層的圖形形狀、尺寸和位置。這一步相當于繪制一個多層次的地圖,每一層代表一個工藝層次,工程師需要準確地在這些圖層上繪制出符合工藝要求的圖形。

規(guī)則檢驗:設(shè)計規(guī)則是集成電路制造商提供的“協(xié)議”,是設(shè)計和工藝之間的接口。規(guī)則檢驗包括以下幾個方面:

設(shè)計規(guī)則檢驗(DRC):確保圖形滿足最小寬度、最小間距等設(shè)計要求。

電氣規(guī)則檢驗(ERC):檢查電路電氣連接是否滿足要求,如電源與地線的正確連接。

版圖與電路圖一致性檢驗(LVS):保證版圖與原始電路圖在功能和邏輯上相一致。

布局布線(Place and Route):EDA工具可以通過自動化的方式幫助工程師進行布局和布線操作。現(xiàn)代EDA工具的自動布線技術(shù)能夠優(yōu)化連線長度、減少電容效應(yīng),從而提高電路性能。

四、版圖設(shè)計規(guī)則

設(shè)計規(guī)則是集成電路版圖設(shè)計的核心準則,它規(guī)范了版圖設(shè)計的各個方面。設(shè)計規(guī)則包括[敏感詞]和相對值兩種標準。

[敏感詞]設(shè)計規(guī)則:這是以實際尺寸為單位的規(guī)定。例如,金屬層的最小寬度可能被限制為100納米,以確保可靠性。

相對值設(shè)計規(guī)則:這是基于比例因子(例如m、n等)來定義的規(guī)則,具體數(shù)值與制造工藝有關(guān)。例如,若規(guī)則規(guī)定某層的寬度w = mA,那么m是與圖形類型有關(guān)的比例因子,而A是基準單位。

設(shè)計規(guī)則還包括以下常見要求:

最小寬度:保證布線不至于因?qū)挾炔蛔愣谥圃旎蚴褂弥袛嗔选?/span>

最小間距:確保不同線之間不會因過近而產(chǎn)生短路。

最短露頭:確保元件不會超出版圖邊界,以利于光刻對齊和封裝。

邊界距離:保證元件之間有足夠的空間,以免相互影響。

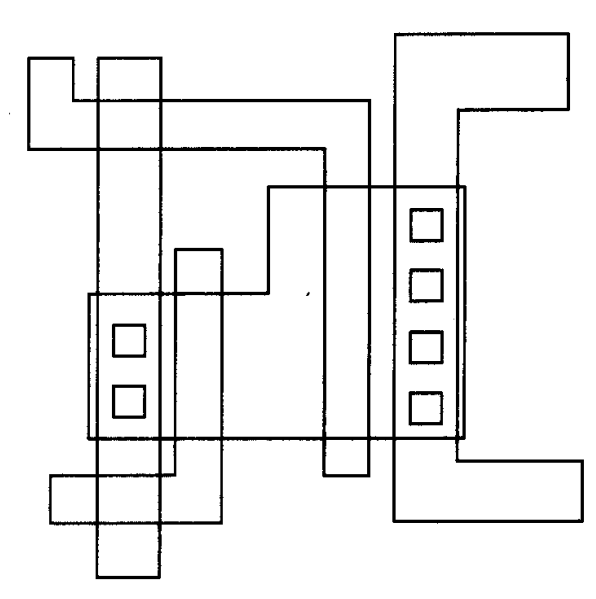

五、曼哈頓幾何形狀

在版圖設(shè)計中,大多數(shù)圖形采用“曼哈頓幾何形狀”,即主要由水平或垂直的直角線段組成的圖形。這種幾何形狀的設(shè)計符合制造工藝的需求,因為集成電路的光刻工藝在處理直角時更具精度與穩(wěn)定性。此外,曼哈頓幾何形狀也便于規(guī)則檢驗和自動布線工具的使用。

六、版圖設(shè)計的挑戰(zhàn)與藝術(shù)性

版圖設(shè)計不僅是一門技術(shù),還是一門藝術(shù)。優(yōu)秀的版圖設(shè)計師需要在有限的空間內(nèi),以精湛的技藝完成復雜電路的布局和布線。他們必須考慮多層次的結(jié)構(gòu)布局,確保電路的美觀和功能性。有經(jīng)驗的版圖設(shè)計師能夠在設(shè)計中融入藝術(shù)性,創(chuàng)作出不僅具備高性能且具視覺美感的版圖。

例如,在設(shè)計存儲單元時,設(shè)計師需要考慮如何排布大量重復單元以節(jié)省空間,并在連線時[敏感詞]化減少信號延時。一個設(shè)計巧妙的存儲單元陣列能夠有效利用空間,極大地提升芯片性能。

七、版圖設(shè)計的未來趨勢

隨著集成電路工藝向更小的制程演進,版圖設(shè)計面臨更多挑戰(zhàn)。未來,以下趨勢將進一步推動版圖設(shè)計的發(fā)展:

更小尺寸的器件和更高集成度:7nm及以下制程的推進使得設(shè)計規(guī)則變得更加嚴格,版圖設(shè)計師需要考慮更多的物理效應(yīng)。

3D IC技術(shù)的發(fā)展:三維集成電路將不同功能的芯片垂直堆疊,這帶來了全新的布局和布線難題,設(shè)計師需要考慮芯片間的熱管理和信號傳輸問題。

智能化和自動化設(shè)計工具:隨著AI技術(shù)的發(fā)展,EDA工具將越來越智能化,可以自動識別并優(yōu)化版圖中的瓶頸,從而降低設(shè)計難度,提高設(shè)計效率。

小結(jié)一下。集成電路版圖設(shè)計是一個兼具技術(shù)性和藝術(shù)性的領(lǐng)域,它不僅要求設(shè)計師在布局、布線和尺寸確定等方面有精湛的技巧,還需要遵循制造工藝的設(shè)計規(guī)則。在EDA工具的輔助下,版圖設(shè)計師能夠在有限的芯片空間內(nèi)實現(xiàn)復雜的電路功能。未來,隨著集成電路技術(shù)的不斷發(fā)展,版圖設(shè)計的挑戰(zhàn)將持續(xù)增加,但也將出現(xiàn)更多創(chuàng)新的工具和方法,為芯片的高性能、高集成度設(shè)計提供支持。

免責聲明:本文采摘自“老虎說芯”,本文僅代表作者個人觀點,不代表薩科微及行業(yè)觀點,只為轉(zhuǎn)載與分享,支持保護知識產(chǎn)權(quán),轉(zhuǎn)載請注明原出處及作者,如有侵權(quán)請聯(lián)系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標官網(wǎng) 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權(quán)所有 粵ICP備20017602號-1