-

- 更新日期: 2024-10-22

- 瀏覽次數: 984

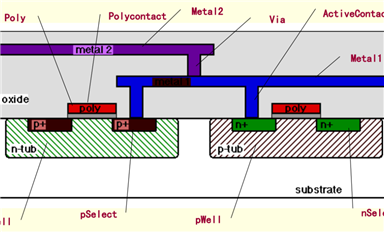

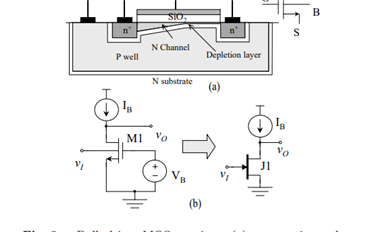

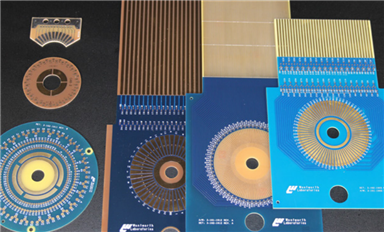

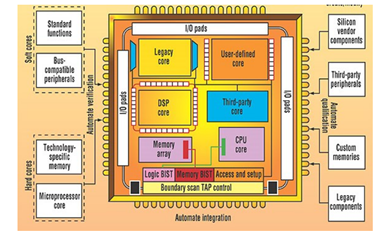

SoC(系統級芯片)與SiP(系統級封裝)兩種技術都是現代集成電路發展的重要里程碑,它們都能實現電子系統的小型化、高效化和集成化。 一、SoC(系統級芯片)和SiP(系統級封裝)的定義及基本思路 SoC(System on Chip)——將整個系統“擠”進一個芯片 SoC 就像一棟高樓,把所有的功能模塊都設計、集成到同一個物理芯片上。SoC的核心思想是將整個電子系統的核心部件,包括處理器(CPU)、存儲器、通信模塊、模擬電路、傳感器接口等多種不同功能模塊全部集成在一個芯片上。SoC的優勢