服務熱線

0755-83044319

發布時間:2022-04-13作者來源:印寧華瀏覽:3568

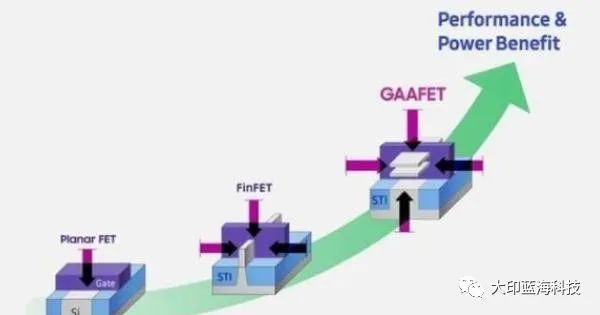

FinFET試圖克服晶體管遇到的最糟糕類型的短溝道效應,同時使芯片能夠以更低的成本實現更高的性能指標。自從半導體取得突破以來,縱觀集成電路設計的歷史,摩爾定律——即一塊硅上的晶體管數量每兩年翻一番,而且將一直保持不變。隨著代工廠開發越來越先進的工藝節點以滿足消費者的需求,當今先進處理器上的晶體管數量達到數百億。這與1970年代中期只有幾千個晶體管的處理器相去甚遠,這在當時是[敏感詞]的。

推動半導體行業發展并使今天的芯片成為可能的關鍵技術趨勢之一是采用FinFET工藝。另一種有前途的技術是環柵(GAA)晶體管。這提供了柵極和溝道之間最顯著的電容耦合。GAA FinFET的問題在于它只是一個臨時解決方案。它可能只持續幾十年。然而,它很可能成為FinFET的未來替代品,至少在有人提出全新的晶體管架構之前是這樣。

什么是FinFET?

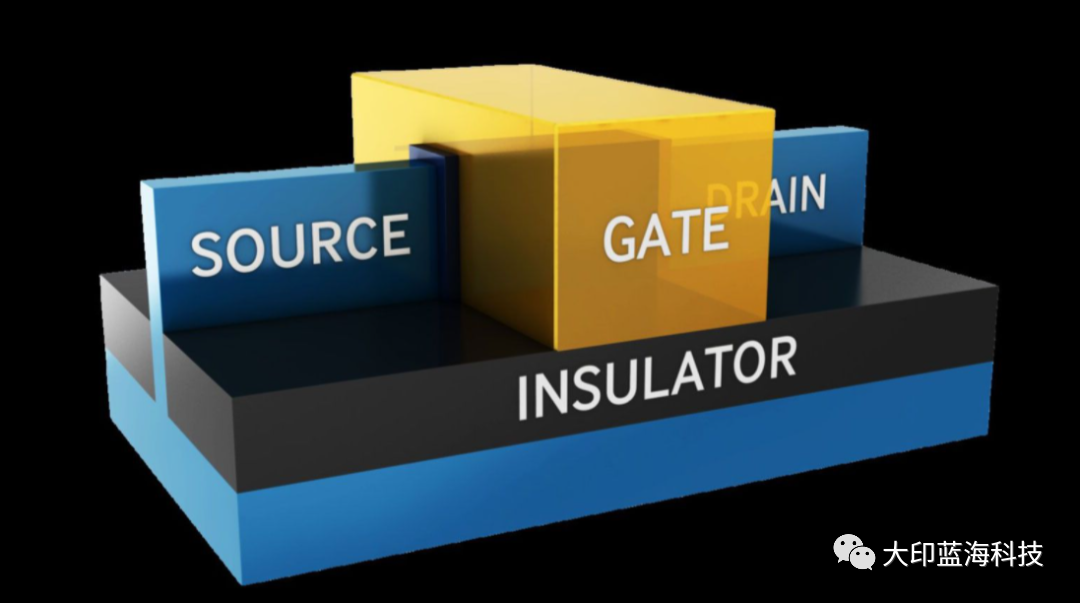

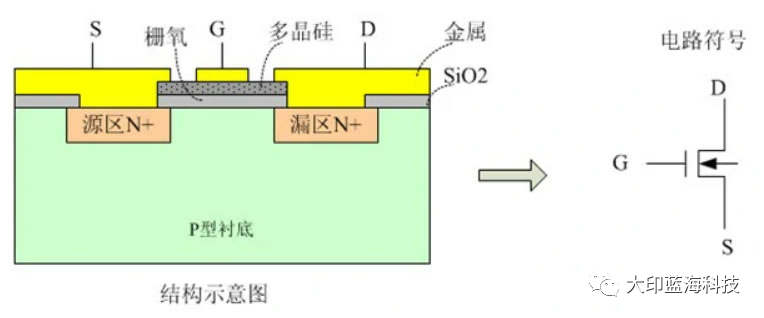

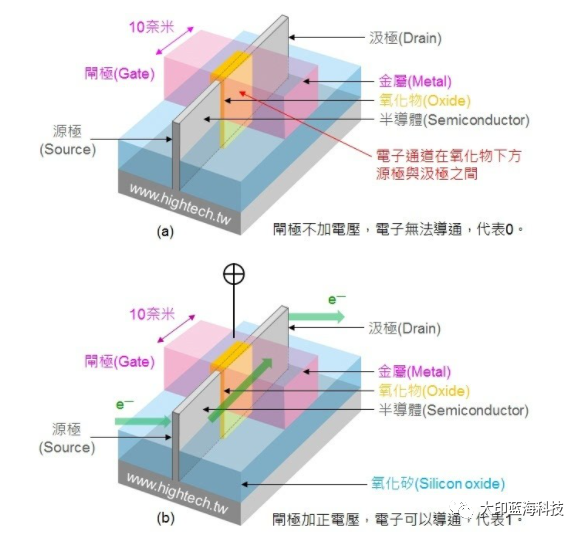

提到FET,學電子的人都比較熟悉,FET就是Field-Effect Transistor,場效應管。FET是一種常見的三端口半導體器件,比較常見的是JFET(結型場效應晶體管)和金屬氧化物場效應管MOSFET。下圖給出了常見的場效應管的工作示意圖,

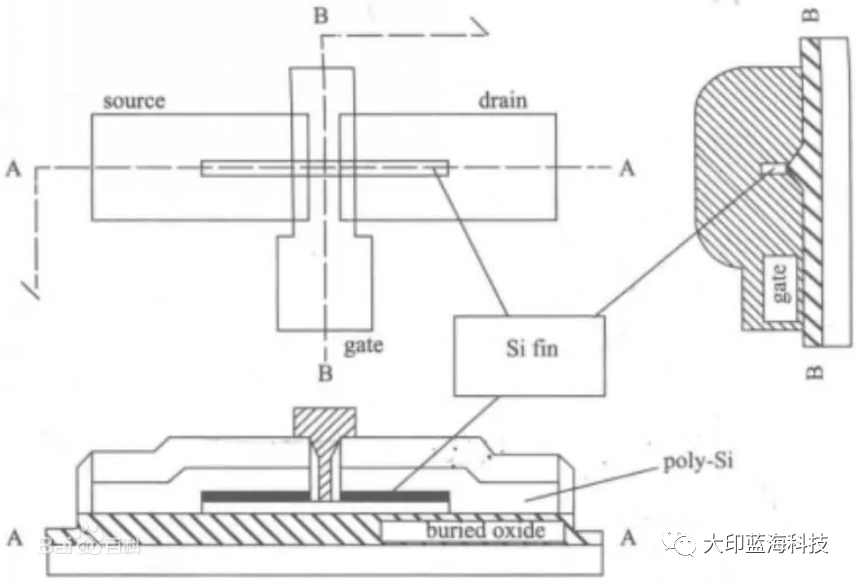

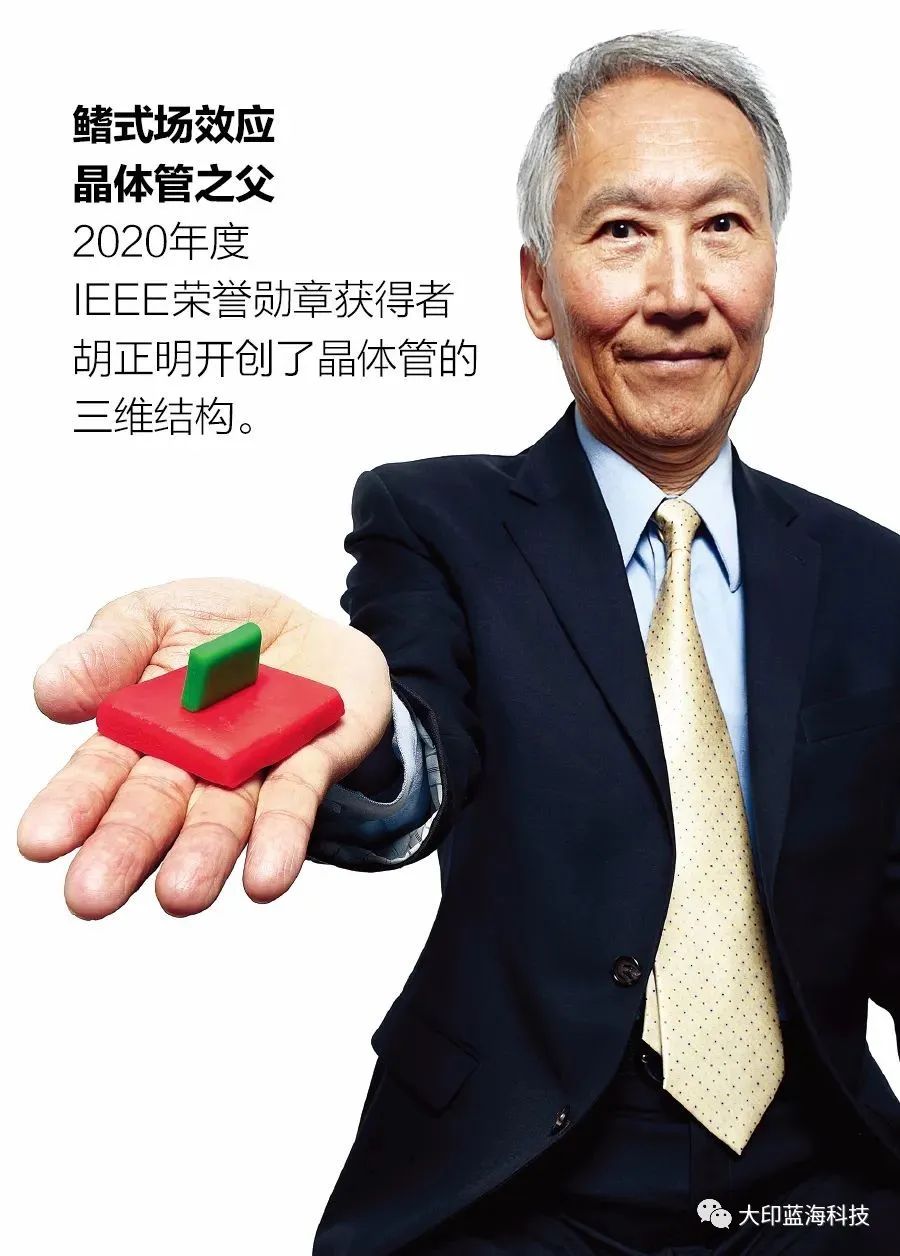

FinFET被稱為鰭式場效應晶體管,是一種新的互補式金屬氧化物半導體晶體管。該項技術的發明人是加州大學伯克利分校的胡正明教授。

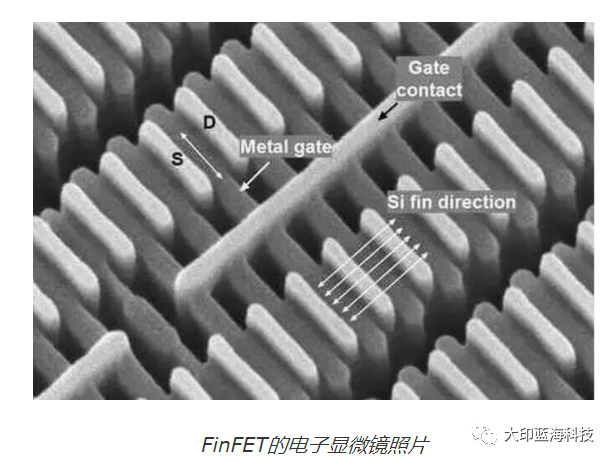

FinFeT與平面型MOSFET結構的主要區別在于其溝道由絕緣襯底上凸起的高而薄的鰭構成,源漏兩極分別在其兩端,三柵極緊貼其側壁和頂部,用于輔助電流控制,這種鰭形結構增大了柵圍繞溝道的面,加強了柵對溝道的控制,從而可以有效緩解平面器件中出現的短溝道效應,大幅改善電路控制并減少漏電流,也可以大幅縮短晶體管的柵長,也正由于該特性,FinFET無須高摻雜溝道,因此能夠有效降低雜質離子散射效應,提高溝道載流子遷移率。

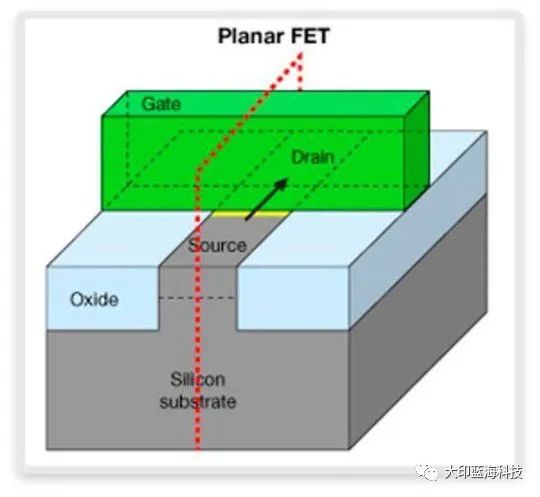

與傳統的二維平面晶體管相比,FinFET(鰭式場效應晶體管)是一種具有高架溝道(Fin)的三維晶體管,柵極環繞該溝道。

臺積電于2002年12月演示了[敏感詞]個僅在0.7伏電壓下工作的25納米FinFET晶體管。然而,直到2012年,[敏感詞]個商用22nmFinFET面世,隨后對FinFET架構的改進使得在提高性能和減少面積方面取得了長足的進步。

由于其結構,FinFET產生較低的泄漏功率并實現更高的器件密度。它們還可以在較低電壓下運行并提供高驅動電流。所有這些加在一起意味著可以在更小的區域內集成更多的性能,從而降低每單位性能的成本。

FinFET與平面晶體管(例如 MOSFET)

出于多種原因,設計人員選擇使用FinFET器件而不是傳統的平面晶體管(如MOSFET)。增加計算能力意味著增加計算密度。當然需要更多的晶體管來實現這一點,這會導致更大的芯片。然而,出于實際原因,保持面積大致相同很重要。獲得更多計算能力的一種方法是縮小晶體管的尺寸,但隨著晶體管尺寸的減小,漏極和源極之間的距離會縮小柵極控制溝道區電流的能力。因此,平面MOSFET會受到短溝道效應的影響。

簡而言之,與傳統平面MOSFET技術相比,FinFET器件表現出卓越的短溝道行為、更短的開關時間和更高的電流密度。

三、FinFET的優缺點

與其他晶體管技術相比,FinFET具有幾個關鍵優勢,使其非常適用于需要更高功率和性能的應用:

(1)更好的渠道控制;

(2)抑制短通道效應;

(3)更快的切換速度;

(4)更高的漏極電流;

(5)較低的開關電壓;

(6)更低的功耗。

當然,也有缺點。它們的一些缺點包括:

(1)電壓閾值難以控制;

(2)三維輪廓導致更高的寄生效應;

(3)非常高的電容;

(4)造價高。

FinFET的溝道一般是輕摻雜甚至是不摻雜的,它避免了離散的額摻雜原子的散射作用,同重摻雜的平面器件相比,其載流子的遷移率會大大提高。FinFET機構增大了柵極對溝道的控制面積,使得柵控能力大大增強,從而可以有效抑制短溝道效應,減小亞閾值泄露電流。亞閾值擺幅S是衡量晶體管開啟與關斷狀態之間相互轉換速率的性能指標,它代表源漏電流變化十倍所需要柵電壓的變化量,S越小意味著開啟關斷速率越快。由于短溝道效應的抑制和柵控能力的增強,FinFET器件可以使用比平面器件更厚的柵氧化物,從而可以減小柵泄露電流。更強的柵控能力允許大幅縮短晶體管的柵長,從而進一步減小面積。

1、綜合看來,與平面器件相比,FINFET結構具有更好的溝道控制能力和更好的亞閾值斜率,可以提供更小的泄露電流和更小的柵極延遲以及更大的電流驅動能力,具有多方面的優勢,在22nm技術代及以下有著良好的應用前景。

2、MOS晶體管是具有漏極、源極、柵極和襯底的4端子器件。圖1顯示了NMOS的3維結構。NMOS晶體管形成在p型硅襯底(也稱為本體)上。在器件的頂部中心部分,形成一個低電阻率的電極,它通過一個絕緣體與本體分開。通常,使用n型或p型重摻雜的多硅作為柵極材料。這里,使用二氧化硅(SiO 2或簡單的氧化物)作為絕緣體。通過將供體雜質植入基板的兩側,形成源極和漏極。

3、對于傳統的MOS結構,隨著溝道長度的縮小,柵極不能完全控制通道,這是不希望看到的。其影響之一是從漏極到源極引起更多的亞閾值泄漏,這從功耗角度來看不是很好。

FinFET的主要特點是,溝道區域是一個被柵極包裹的鰭狀半導體。沿源漏方向的鰭的長度,為溝道長度。柵極包裹的結構增強了柵的控制能力, 對溝道提供了更好的電學控制,從而降低了漏電流,抑制短溝道效應。 然而FinFET有很多種,不同的FinFET有不同的電學特性。

下面根據襯底類型、溝道的方向、柵的數量、柵的結構,分別給予介紹。SOI FinFET 和體FinFET。根據FinFET襯底,FinFET可以分成兩種。一種是SOI FinFET,一種是體FinFET。FinFET形成在體硅襯底上。由于制作的工藝不同,相比于SOI襯底,體硅襯底具有低缺陷密度,低成本的優點。此外,由于SOI襯底中埋氧層的熱傳導率較低,體硅襯底的散熱性能也要優于SOI襯底。

Buk FinFET,SOI FinFET具有近似的寄生電阻、寄生電容,從而在電路水平上可以提供相似的功率性能。但是 SOI 襯底的輕鰭摻雜FinFET,相比于Buk FinFET,表現出較低的節電容,更高的遷移率和電壓增益的電學性能。

對于場效應管,我們最常用的是MOSFET,全稱是金屬氧化物半導體場效應管:Metal Oxide Semiconductor Field Effect Transistor。

MOSFET在1960年由貝爾實驗室(Bell Lab.)的D. Kahng和 Martin Atalla首次實作成功,這種元件的操作原理和1947年蕭克萊(William Shockley)等人發明的雙載流子結型晶體管(Bipolar Junction Transistor,BJT)截然不同,且因為制造成本低廉與使用面積較小、高整合度的優勢,在大型集成電路(Large-Scale Integrated Circuits,LSI)或是超大型集成電路(Very Large-Scale Integrated Circuits,VLSI)的領域里,重要性遠超過BJT。

但是MOSFET發明至今已有六十多年歷史,隨著半導體制程工藝的進步,MOSFET的限制越來越明顯。我們知道,在 MOSFET 中,柵極長度(Gate length)大約 10 奈米,是所有構造中最細小也最難制作的,因此我們常常以柵極長度來代表半導體工藝的進步程度,這就是所謂的工藝線寬。

柵極長度會隨工藝技術的進步而變小,從早期的 0.18 微米、0.13 微米,進步到 90 納米、65 納米、45 納米、22 納米,到目前[敏感詞]工藝 10 納米。當柵極長度愈小,則整個 MOSFET 就愈小,而同樣含有數十億個 MOSFET 的芯片就愈小,封裝以后的集成電路就愈小,最后做出來的手機就愈小。

10 納米到底有多小呢?細菌大約 1 微米,病毒大約 100 納米,換句話說,人類現在的工藝技術可以制作出只有病毒 1/10(10 納米)的結構,厲害吧!但是當柵極長度縮小到 20 納米以下的時候,遇到了許多問題,其中最麻煩的是當閘極長度愈小,源極和漏極的距離就愈近,柵極下方的氧化物也愈薄,電子有可能偷偷溜過去產生漏電(Leakage);

另外一個更麻煩的問題,原本電子是否能由源極流到漏極是由閘極電壓來控制的,但是柵極長度愈小,則柵極與通道之間的接觸面積(圖一紅色虛線區域)愈小,也就是閘極對通道的影響力愈小,要如何才能保持閘極對通道的影響力(接觸面積)呢?因此美國加州大學伯克萊分校胡正明、 Tsu-Jae King-Liu、Jeffrey Bokor 等三位教授發明了鰭式場效晶體管(Fin Field Effect Transistor,FinFET),把原本 2D 構造的 MOSFET 改為 3D 的 FinFET,如圖所示,因為構造很像魚鰭 ,因此稱為鰭式(Fin)。

由圖中可以看出原本的源極和漏極拉高變成立體板狀結構,讓源極和漏極之間的通道變成板狀,則柵極與通道之間的接觸面積變大了(圖二[敏感詞]的氧化物與下方接觸的區域明顯比圖一紅色虛線區域還大),這樣一來即使柵極長度縮小到 20 納米以下,仍然保留很大的接觸面積,可以控制電子是否能由源極流到汲極,因此可以更妥善的控制電流,同時降低漏電和動態功率耗損,所謂動態功率耗損就是這個 FinFET 由狀態 0 變 1 或由 1 變 0 時所消耗的電能,降低漏電和動態功率耗損就是可以更省電的意思。

FinFET是柵極長度縮小到 20 納米以下的關鍵,擁有這個技術的工藝與專利,才能確保未來在半導體市場上的競爭力。當然場效應管也不是一成不變的,FinFET也不會是最終的選項,其演進一直在進行中。

在過去的 17 年中,CMOS 技術在制造和建筑中使用的材料方面取得了重大進展。[敏感詞]個巨大飛躍是在 90 nm 技術節點引入應變工程。隨后的步驟是具有 45 nm 高 k 電介質的金屬柵極,以及 22 nm 節點的 FinFET 架構。2012 年標志著[敏感詞]個商用 22nm FinFET 的誕生。FinFET 架構的后續改進提高了性能并減少了面積。FinFET 的 3D 特性具有許多優勢,例如增加鰭片高度以在相同的占位面積下獲得更高的驅動電流。

下圖顯示了 MOSFET 結構的演變:雙柵、三柵、pi 柵、omega 柵和環柵。由于結構簡單且易于制造,雙柵極和三柵極 FinFET 很常見。盡管 GAA 器件是在 FinFET 之前提出的,但后者更適合執行生產。

未來,到底屬于那種技術,讓我們拭目以待,并努力向前。

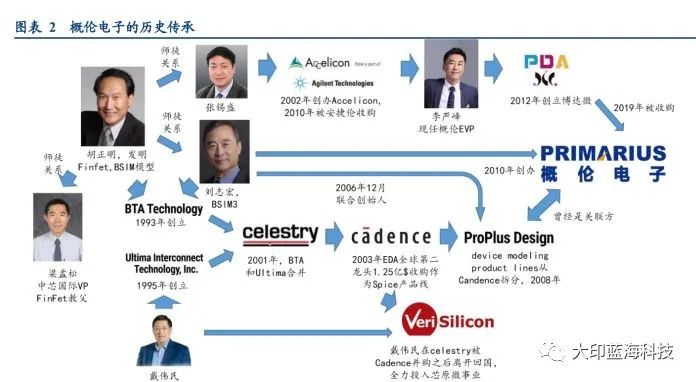

國產EDA新銳概倫電子與FinFET之父-胡正明院士

雖然概倫電子成立于2010年,但是在成立之處就和創始人的關聯公司ProPlus有過深度的技術/人才合作,而ProPlus正和劉志宏和胡正明教授在1993年創立的BTA有傳承關系。

概倫電子在2020年并購的博達微科技也可以追溯至胡正明教授:

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1