服務(wù)熱線

0755-83044319

發(fā)布時間:2022-03-17作者來源:薩科微瀏覽:2860

傳統(tǒng)上,IC芯片與外部的電氣連接是用金屬引線以鍵合的方式把芯片上的I/O連至封裝載體并經(jīng)封裝引腳來實現(xiàn)。隨著IC芯片特征尺寸的縮小和集成規(guī)模的擴大,I/O的間距不斷減小、數(shù)量不斷增多。當(dāng)I/O間距縮小到70 um以下時,引線鍵合技術(shù)就不再適用,必須尋求新的技術(shù)途徑。晶元級封裝技術(shù)利用薄膜再分布上藝,使I/O可以分布在IC芯片的整個表面上而不再僅僅局限于窄小的IC芯片的周邊區(qū)域,從而解決了高密度、細(xì)間距I/O芯片的電氣連接問題。

在眾多的新型封裝技術(shù)中,晶元級封裝技術(shù)[敏感詞]創(chuàng)新性、最受世人矚目,是封裝技術(shù)取得革命性突破的標(biāo)志。晶元級封裝技術(shù)以晶元為加工對象,在晶元上同時對眾多芯片進(jìn)行封裝、老化、測試,最后切割成單個器件。它使封裝尺寸減小至IC芯片的尺寸,生產(chǎn)成本大幅度下降。晶元級封裝技術(shù)的優(yōu)勢使其一出現(xiàn)就受到極大的關(guān)注并迅速獲得巨大的發(fā)展和廣泛的應(yīng)用。在移動電話等便攜式產(chǎn)品中,已普遍采用晶元級封裝型的EPROM、IPD(集成無源器件)、模擬芯片等器件。采用晶元級封裝的器件門類正在不斷增多,晶元級封裝技術(shù)是一項正在迅速發(fā)展的新技術(shù)。

為了提高晶元級封裝的適用性并擴大其應(yīng)用范圍,人們正在研究和開發(fā)各種新型技術(shù)同時解決產(chǎn)業(yè)化過程中出現(xiàn)的問題,開展對晶元級封裝技術(shù)的現(xiàn)狀、應(yīng)用和發(fā)展進(jìn)行研究。

晶元級封裝

WLP的最初萌芽是由用于移動電話的低速I/O(low-I/O)、低速晶體管元器件制造帶動起來的,如無源的片上感應(yīng)器和功率傳輸ICs等,目前WLP正處于發(fā)展階段,受到藍(lán)牙、GPS(全球定位系統(tǒng))元器件以及聲卡等應(yīng)用的推動,需求正在逐步增長。當(dāng)發(fā)展到3G手機生產(chǎn)階段時,預(yù)計各種各樣的手機內(nèi)容全新應(yīng)用將成為WLP的又一個成長動力,其中包括電視調(diào)諧器(TV tuners)、調(diào)頻發(fā)射器(FM transmitters)以及堆棧存儲器等。隨著存儲器件制造商開始逐步實施WLP,將引領(lǐng)整個行業(yè)的模式化變遷。

目前,晶元級封裝技術(shù)已廣泛用于閃速存儲器、EEPROM、高速DRAM、SRAM、LCD驅(qū)動器、射頻器件、邏輯器件、電源/電池管理器件和模擬器件(穩(wěn)壓器、溫度傳感器、控制器、運算放大器、功率放大器)等領(lǐng)域。晶元級封裝主要采用薄膜再分布技術(shù)、凸點形成兩大基礎(chǔ)技術(shù)。前者用于把沿芯片周邊分布的焊接區(qū)域轉(zhuǎn)換為在芯片表面上按平面陣列形式分布的凸點焊區(qū)。后者則用于在凸點焊區(qū)上制作凸點,形成焊球陣列。

薄膜再分布WL-CSP

膜再分布WL-CSP是當(dāng)今使用最普遍的工藝。因為它的成本較低,非常適合大批量、便攜式產(chǎn)品板級應(yīng)用可靠性標(biāo)準(zhǔn)的要求。如同其它的WLP一樣,薄膜再分布WL-CSP的晶元仍采用常規(guī)晶元工藝制作。在晶元送交WLP供貨商之前,要對晶元進(jìn)行測試,以便對電路進(jìn)行分類和繪出合格電路的晶元圖。晶元在再分布之前,先要對器件的布局進(jìn)行評估,以確認(rèn)該晶元是否適合于進(jìn)行焊球再分布。

一種典型的再分布工藝,最終形成的焊料凸點呈面陣列布局,該工藝中,采用BCB作為再分布的介質(zhì)層,Cu作為再分布連線金屬,采用濺射法淀積凸點底部金屬層(UBM),絲網(wǎng)印刷法淀積焊膏并回流,其中底部金屬層工藝對于減少金屬間化合反應(yīng)和提高互連可靠性來說十分關(guān)鍵。

再分布工藝就是在器件表面重新布置I/O焊盤。圖3示出了鍵合閃速存儲器上再分布的情形。從圖中可見,閃速存儲器芯片四邊上的原有焊盤轉(zhuǎn)換成了凸點陣列。在此實例中,器件表面使用了兩層介質(zhì)層,中間夾有的一層再分布金屬化層用于改變I/O的分布。在這工序之后,電鍍上焊球凸點,于是芯片就變成了WLP產(chǎn)品。

將引線鍵合焊盤設(shè)計再分布成焊球陣列焊盤的缺點是:生產(chǎn)的WLP產(chǎn)品在器件設(shè)計、結(jié)構(gòu)或制造成本方面不可能是[敏感詞]。但是,一旦證明其技術(shù)上可行,那么就可對這種電路重新設(shè)計,于是就可以消除外加再分布。這種情況已成共識。為此,特別定義了一種雙相判定程序。下一代的變化可能是在芯片最后金屬層內(nèi)集成再分布層,或者是一種用以改進(jìn)性能的最短信號線的新設(shè)計。

薩科微SLKOR產(chǎn)品 線性穩(wěn)壓芯片 SL78L05

重新設(shè)計可能需要補充新的軟件工具。由于重新設(shè)計可消除外加的再分布工序和相關(guān)工藝,因此,重新設(shè)計的信號、電源和接地線的結(jié)構(gòu)非常低廉。聚合物用于硅片平坦化,對芯片提供必要的保護(hù),以及用作標(biāo)準(zhǔn)的表面涂敖。對于薄膜再分布WLP來說,單層聚合物WLP方法不失為一種成本--效益更佳的設(shè)計。

晶元級微凸點的制作

引線鍵合自50年前誕生以來,一直被認(rèn)為是一種通用的、可靠的互連技術(shù)。但是,隨著移動通信、因特網(wǎng)電子商務(wù)無線接入系統(tǒng)及藍(lán)牙系統(tǒng)與傘球定位系統(tǒng)(GPS)技術(shù)的高速發(fā)展,手機已成為高密度存儲器最強、最快的增長動力,它正在取代PC成為高密度存儲器的技術(shù)驅(qū)動,對更低成本、更小外形、更高速的器件性能、更長的電池壽命、更好的散熱、"綠色"工藝和更高的器件可靠性的需求,使得設(shè)計人員把目光投向倒裝芯片凸點互連技術(shù),以取代傳統(tǒng)的引線鍵合技術(shù)。

鉛錫凸點技術(shù)發(fā)展的關(guān)鍵技術(shù)推動力來自持續(xù)的器件尺寸緊縮。在130nm技術(shù)標(biāo)準(zhǔn)下,約有30%的邏輯芯片需要凸點技術(shù)。但是在90 nm技術(shù)標(biāo)準(zhǔn)下,這一數(shù)據(jù)躍升到60%,當(dāng)發(fā)展到了65 nm器件量產(chǎn)制造時,金凸點技術(shù)的需求則攀升至80%以上。

WLP以BGA技術(shù)為基礎(chǔ),是一種經(jīng)過改進(jìn)和提高的CSP。有人又將WLP稱為晶元級芯片尺寸封裝(WLP-CSP)它不僅充分體現(xiàn)了BGA、CSP的技術(shù)優(yōu)勢,而且是封裝技術(shù)取得革命性突破的標(biāo)志。晶元級封裝技術(shù)采用批量生產(chǎn)工藝制造技術(shù),可以將封裝尺寸減小至IC芯片的尺寸,生產(chǎn)成本大幅度下降,并且把封裝與芯片的制造融為一體,將徹底改變芯片制造業(yè)與芯片封裝業(yè)分離的局面。正因為晶元級封裝技術(shù)有如此重要的意義,所以,它一出現(xiàn)就受到極大的關(guān)注并迅速獲得巨大的發(fā)展和廣泛的應(yīng)用。

凸點下金屬化層(UBM)

在倒裝芯片互連方式中,UBM層是IC上金屬焊盤和金凸點或焊料凸點之間的關(guān)鍵界面層。該層是倒裝芯片封裝技術(shù)的關(guān)鍵因素之一,并為芯片的電路和焊料凸點兩方面提供高可靠性的電學(xué)和機械連接。凸點和I/O焊盤之間的UBM層需要與金屬焊盤和晶圓鈍化層具有足夠好的粘結(jié)性;在后續(xù)工藝步驟中保護(hù)金屬焊盤;在金屬焊盤和凸點之間保持低接觸電阻;可以作為金屬焊盤和凸點之間有效的擴散阻擋層;并且可以作為焊料凸點或者金凸點沉積的種子層。

UBM層通常是在整個晶圓表面沉積多層金屬來實現(xiàn)。用于沉積UBM層的技術(shù)包括蒸發(fā)、化學(xué)鍍和濺射沉積。在高級封裝中,無論從成本還是技術(shù)角度考慮,晶圓凸點制作都非常關(guān)鍵。在晶圓凸點制作中,金屬沉積占到全部成本的50%以上。晶圓凸點制作中最為常風(fēng)的金屬沉積步驟是凸點下金屬化層(UBM)的沉積和凸點本身的沉積,一般通過電鍍工藝實現(xiàn)。

電鍍技術(shù)可以實現(xiàn)很窄的凸點節(jié)距并維持高產(chǎn)率。并且該項技術(shù)應(yīng)用范圍也很廣,可以制作不同尺寸、節(jié)距和幾何形狀的凸點,電鍍技術(shù)已經(jīng)越來越廣泛地在晶圓凸點制作中被采用,成為[敏感詞]實用價值的方案。

首先在晶圓上完成UBM層的制作。然后沉積厚膠并曝光,為電鍍焊料形成模板。電鍍之后,將光刻膠去除并刻蝕掉暴露出來的UBM層。最后一部工藝是再流,形成焊料球。電鍍制作微凸點的詳細(xì)工藝步驟為:

▲在晶元上蒸發(fā)/濺射籽晶導(dǎo)電層(seed conductive layer)的金屬層;

▲在晶元上旋轉(zhuǎn)涂覆一層光刻膠;

▲光刻電極窗口陣列圖形;

▲通過光刻膠上小孔電鍍金屬微嵌入體;

▲去除光刻膠;

▲刻蝕已暴露的籽晶導(dǎo)電層。

▲在金屬嵌入體上涂覆厚層光刻膠;

▲套刻出Au凸點;

▲刻蝕掉部分厚膠,使金屬嵌入體的突出部分得以顯現(xiàn);

▲電鍍Au凸點;

▲在嵌入體頂部淀積一層很薄的Au或Cu層。

共面性是指晶元內(nèi)所有凸點高度的一致性,它在倒裝芯片鍵合工藝中有著嚴(yán)格的要求。在倒裝芯片鍵合中,凸點的高度變化會導(dǎo)致力的不均勻分布、芯片碎裂和電學(xué)開路。對于凸點共面性的典型要求是在整個芯片的凸點的高度差不能大于5μm。

厚膜光刻

晶圓級工藝技術(shù),如微小間距晶圓凸點、引線焊盤重分布和集成無源元件等為很多應(yīng)用提供了方便的解決方案。目前,許多IC和MEMS的器件已經(jīng)應(yīng)用了這些技術(shù)。利用這些技術(shù),可以在晶圓級實現(xiàn)器件封裝和測試,再進(jìn)行其后的切割工序。通常高級封裝技術(shù)涉及5~100 μm的厚膜工藝,如厚膠旋涂、對表面有較大起伏的厚膠均勻曝光以及獲得非常陡峭的厚膠側(cè)壁。等倍式全場曝光系統(tǒng)是一種可以滿足這種需求的設(shè)備解決方案,其產(chǎn)量高、自對準(zhǔn)成本低,在厚膜光刻領(lǐng)域成為投影式步進(jìn)機[敏感詞]競爭力的系統(tǒng)。

晶圓級封裝工藝包括金屬化、光刻、電介質(zhì)淀積和厚膜光刻膠旋涂、焊料淀積和回流焊接。圖形化工藝通常涉及到用幾層金屬制作用于凸點基礎(chǔ)的凸點下金屬層(UBM)。凸點和晶圓連接的導(dǎo)電性要很好,鈍化層和凸點下金屬層需要有很好的附著性。光刻膠圖形化的標(biāo)準(zhǔn)工藝流程包括清洗、涂膠、前烘、曝光、后烘、顯影和堅膜。每步工藝都需要定義一套參數(shù),這些參數(shù)對以后的工序有所影響。光刻膠圖形化完成之后,通過電鍍或蒸鍍方法向空穴里填充焊料或金。下一步就是去除光刻膠,在烤爐內(nèi)進(jìn)行回流工藝,將柱狀凸點轉(zhuǎn)換成球形凸點。

厚光刻膠涂層將保留在芯片上作為制造金屬焊點微模具的掩模。重分布涂層可以改裝成凸點版圖,或者作為周邊焊盤和面積分布焊盤陣列的連線,這些焊盤陣列由5~100 μm厚的具有不同電學(xué)、化學(xué)、機械和熱屬性多晶硅膜制成。隔離再分布區(qū)域跡線需要具有高強度、高熱穩(wěn)定性和低絕緣系數(shù)的材料。這些材料已經(jīng)研發(fā)成功,其中一類材料稱為聚酰亞胺(如杜邦公司研制的PI系列),另外一種絕緣材料是美國道化學(xué)公司(Dow chemicals)的苯丙環(huán)丁烯(Cyclotene;BCB)。PI和BCB廣泛應(yīng)用于倒裝芯片凸點封裝及其他封裝工藝。

使用厚膜光刻膠的焊盤、凸點和球下金屬層結(jié)構(gòu)的微特征模具可以滿足WLP中的不同需要。盡管普遍應(yīng)用的金屬化材料是錫鉛、金和銅,但是也可應(yīng)用其他幾種材料來實現(xiàn)。用于標(biāo)準(zhǔn)化應(yīng)用的材料要求具有高分辨率圖形轉(zhuǎn)換和易于剝離的屬性。很多實際應(yīng)用需要光刻膠厚度超過100μm。為了能獲得這樣的厚度,制造商研制出合適的涂層材料。

為了滿足這些需要,制造商們研制出相應(yīng)的材料和工藝設(shè)備。很多材料可以在標(biāo)準(zhǔn)的半導(dǎo)體工藝設(shè)備上實現(xiàn)"薄"光刻膠涂層(即2-10 μm)。AZP4330(安智電子材料集團)和Shipley's 955(Rohm&Haas公司/Shipley公司)光刻膠用于實現(xiàn)5~100μm光刻膠膜層厚度。利用多層涂層工藝可以實現(xiàn)25 μm膜厚的光刻膠涂層,但這將會增加生產(chǎn)時間和成本。AZ P4620和SPR 220單層可以實現(xiàn)25 μm厚度。對于更厚的涂層,材料和厚度的選擇范圍變得更小。當(dāng)用單層淀積得到所需的光刻膠涂層時,在成本上會有很多益處。因此,研制單層50 μm及以上厚度的光刻膠材料是非常必要的。例如JSR THB-611P和安智電子材料集團的AZPLP100XT等材料可以實現(xiàn)單層60 μm及以上厚度的光刻膠涂層。最近的研究工作主要是利用AZ9260實現(xiàn)單層65 μm厚度的光刻膠涂層和利用AZ50XT實現(xiàn)單層100 μm厚度的光刻膠。

厚膜工藝對于系統(tǒng)有一些特殊的要求。對準(zhǔn)系統(tǒng)須能在整個膠厚范圍和晶圓表面起伏的特定高度均勻的識別作為對準(zhǔn)標(biāo)記的幾何圖案。由于曝光源利用平行光曝光而不依賴焦點,因此可以利用接近式光刻機結(jié)合陰影曝光原理來實現(xiàn)。光刻過程對于接近式掩模對準(zhǔn)曝光機的要求包括:高強度、高均勻性、紫外光的波長與光刻膠的敏感波長相吻合、亞微米級的對準(zhǔn)精度和在曝光過程中掩模和晶圓之間保持準(zhǔn)確可控且一致的間隙。

EVG公司的NanoAlign技術(shù)以[敏感詞]的對準(zhǔn)精度和分辨率以及[敏感詞]的使用成本為設(shè)計理念來凸現(xiàn)全場曝光技術(shù)的優(yōu)勢。目前,其公司的所有曝光機已經(jīng)應(yīng)用了此項技術(shù)。其目標(biāo)包括了主動異常控制和亞100 nm動態(tài)對準(zhǔn)分辨率。其設(shè)備包括從標(biāo)準(zhǔn)型號改進(jìn)而來的專門涂膠設(shè)備與接觸/接近式曝光機。[敏感詞]型的200 mm EVG6200 Infinity和300 mm EVG IQ Aligner曝光機擁有良好的靈活性與友好的客戶界面,可以充分滿足需要厚膠工藝的φ200 mm與φ300 mm晶圓的工業(yè)生產(chǎn)。

晶元減薄

芯片減薄技術(shù),在疊層式芯片封裝技術(shù)方面是至關(guān)重要的,因為它降低了封裝貼裝高度,并能夠使芯片疊加而不增加疊層式芯片系統(tǒng)方面的總高度。智能卡和RFID是體現(xiàn)薄型晶元各項要求的重要部分最薄的單芯片應(yīng)用形式。較薄的芯片可增加熱循環(huán)可靠性,且支持薄形產(chǎn)品。但芯片薄到什么程度取決于晶元直徑和WLP工藝,其原因是:薄的晶元表面容易產(chǎn)出損傷,引起微裂紋,以及在其后的操作中造成晶元破裂。由于晶元背面研磨是晶元加工工藝的最終步驟,而晶元要減薄到什么程度卻受WLP工藝限制。因此,把晶元級封裝看作是晶元工藝的延伸,在設(shè)計晶元工藝時應(yīng)考慮到封裝工藝步驟的適用范圍。

硅與安裝基板熱膨脹系數(shù)匹配不良是封裝焊料球在熱循環(huán)試驗及現(xiàn)場使用中產(chǎn)生疲勞失效的重要原因。另外,這種失效也與每個元件自身的強度如何密切相關(guān)。芯片越薄,柔性也越好,焊料球抗疲勞的性能必將得到提高。因此,將晶元減薄并由此減小芯片厚度,也是改進(jìn)焊料凸點可靠性的重要措施之一。在晶元級封裝加工之前減薄晶元,容易使晶元變形甚至破碎,這是不可取的。在晶元級封裝加工完成之后進(jìn)行晶元減薄是一種較好的辦法,但實施起來比較困難。供晶元級封裝制造用的晶元和減薄技術(shù)及設(shè)備正在開發(fā)之中。

晶元級封裝的優(yōu)勢

晶元級封裝以BGA技術(shù)為基礎(chǔ),是一種經(jīng)過改進(jìn)和提高的CSP,充分體現(xiàn)了BGA、CSP的技術(shù)優(yōu)勢。它具有許多獨特的優(yōu)點:

①封裝加工效率高,它以晶元形式的批量生產(chǎn)工藝進(jìn)行制造;

②具有倒裝芯片封裝的優(yōu)點,即輕、薄、短、小;

③晶元級封裝生產(chǎn)設(shè)施費用低,可充分利用晶元的制造設(shè)備,無須投資另建封裝生產(chǎn)線;

④晶元級封裝的芯片設(shè)計和封裝設(shè)計可以統(tǒng)一考慮、同時進(jìn)行,這將提高設(shè)計效率,減少設(shè)計費用;

⑤晶元級封裝從芯片制造、封裝到產(chǎn)品發(fā)往用戶的整個過程中,中間環(huán)節(jié)大大減少,周期縮短很多,這必將導(dǎo)致成本的降低;

⑥晶元級封裝的成本與每個晶元上的芯片數(shù)量密切相關(guān),晶元上的芯片數(shù)越多,晶元級封裝的成本也越低。晶元級封裝是尺寸最小的低成本封裝。晶元級封裝技術(shù)是真正意義上的批量生產(chǎn)芯片封裝技術(shù)。

WLP的優(yōu)勢在于它是一種適用于更小型集成電路的芯片級封裝(CSP)技術(shù),由于在晶元級采用并行封裝和電子測試技術(shù),在提高產(chǎn)量的同時顯著減少芯片面積。由于在晶元級采用并行操作進(jìn)行芯片連接,因此可以大大降低每個I/O的成本。此外,采用簡化的晶元級測試程序?qū)M(jìn)一步降低成本。利用晶元級封裝可以在晶元級實現(xiàn)芯片的封裝與測試。

晶元級封裝技術(shù)的發(fā)展趨勢

晶元級封裝技術(shù)要努力降低成本,不斷提高可靠性水平,擴大在大型IC方面的應(yīng)用。在焊球技術(shù)方面,將開發(fā)無Pb焊球技術(shù)和高Pb焊球技術(shù)。隨著IC晶元尺寸的不斷擴大和工藝技術(shù)的進(jìn)步,IC廠商將研究與開發(fā)新一代晶元級封裝技術(shù),這一代技術(shù)既能滿足φ300 mm晶元的需要,又能適應(yīng)近期出現(xiàn)的銅布線技術(shù)和低介電常數(shù)層間介質(zhì)技術(shù)的要求。此外,還要求提高晶元級封裝處理電流的能力和承受溫度的能力。WLBI(晶元級測試和老化)技術(shù)也是需要研究的重要課題。WLBI技術(shù)是要在IC晶元上直接進(jìn)行電氣測試和老化,這對晶元級封裝簡化工藝流程和降低生產(chǎn)成本都具有重要的意義。

結(jié)束語

晶元級封裝技術(shù)是低成本的批量生產(chǎn)芯片封裝技術(shù)。晶元級封裝與芯片的尺寸相同,是最小的微型表面貼裝器件。由于晶元級封裝的一系列優(yōu)點,晶元級封裝技術(shù)在現(xiàn)代電子裝置小型化、低成本化需求的推動下,正在蓬勃向前發(fā)展。當(dāng)前,晶元級封裝技術(shù)通常適用于I/O數(shù)低的小尺寸芯片。業(yè)界還需要開發(fā)新的技術(shù),降低生產(chǎn)成本,發(fā)展大尺寸芯片的晶元級封裝和精細(xì)節(jié)距焊球陣列晶元級封裝。

現(xiàn)代電子裝置選擇封裝類型時,既要滿足設(shè)計要求又要成本[敏感詞]。現(xiàn)有水平的晶元級封裝還只是一種可供選擇的封裝類型。要使晶元級封裝技術(shù)成為未來量大面廣的產(chǎn)品主流制造技術(shù),還有許多工作要做。把半導(dǎo)體芯片和WLP封裝結(jié)合起來設(shè)計,對WLP器件的布局無疑會帶來好處,并可改善器件性能。在WLP中,由于晶元上的所有器件的封裝步驟都是同時進(jìn)行的,成批加工可降低封裝成本。(本文摘自《電子工業(yè)專用設(shè)備》 )

附:Fan-in和Fan-out的區(qū)別

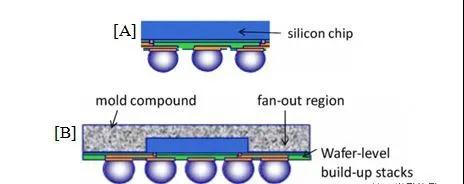

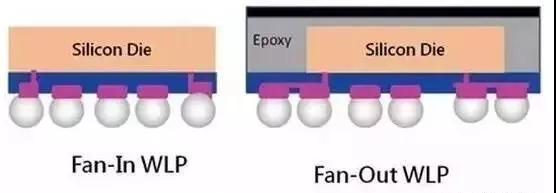

從技術(shù)特點上看,晶圓級封裝主要分為Fan-in和Fan-out兩種。傳統(tǒng)的WLP封裝多采用Fan-in型態(tài),應(yīng)用于低接腳(Pin)數(shù)的IC。但伴隨IC訊號輸出接腳數(shù)目增加,對錫球間距(Ball Pitch)的要求趨于嚴(yán)格,加上印刷電路板(PCB)構(gòu)裝對于IC封裝后尺寸以及訊號輸出接腳位置的調(diào)整需求,因此變化衍生出擴散型(Fan-out)與Fan-in加Fan-out等各式新型WLP封裝型態(tài),其制程甚至跳脫傳統(tǒng)WLP封裝概念。

根據(jù)Amkor中國區(qū)總裁周曉陽介紹:采用Fan-in封裝的芯片尺寸和產(chǎn)品尺寸在二維平面上是一樣大的,芯片有足夠的面積把所有的I/O接口都放進(jìn)去。而當(dāng)芯片的尺寸不足以放下所有I/O接口的時候,就需要Fan-out,當(dāng)然一般的Fan-out 在面積擴展的同時也加了有源和/或無源器件以形成SIP。

首先談一下扇入型。

根據(jù)麥姆斯咨詢的一份報告顯示。扇入型封裝技術(shù)已經(jīng)成功獲得應(yīng)用,并穩(wěn)定增長了十余年。由于其固有的、無可比擬的最小封裝尺寸和低成本相結(jié)合的優(yōu)勢,至今仍極具吸引力。憑借這些優(yōu)勢,它逐漸滲透進(jìn)入受尺寸驅(qū)動的手持設(shè)備和平板電腦市場,并在這些設(shè)備領(lǐng)域仍保持旺盛的生命力。據(jù)估計,目前有超過90%的扇入型封裝技術(shù)應(yīng)用在手機領(lǐng)域。談及扇入型封裝技術(shù)應(yīng)用,如今高端智能手機內(nèi)所有的封裝器件中,超過30%采用了扇入型封裝。因此,扇入型封裝技術(shù)在手機領(lǐng)域還處于商業(yè)黃金期。

盡管扇入型封裝技術(shù)的增長步伐到目前為止還很穩(wěn)定,但是全球半導(dǎo)體市場的轉(zhuǎn)變,以及未來應(yīng)用不確定性因素的增長,將不可避免的影響扇入型封裝技術(shù)的未來前景。隨著智能手機出貨量增長從2013年的35%下降至2016年的8%,預(yù)計到2020年這一數(shù)字將進(jìn)一步下降至6%,智能手機市場引領(lǐng)的扇入型封裝技術(shù)應(yīng)用正日趨飽和。盡管預(yù)期的高增長并不樂觀,但是智能手機仍是半導(dǎo)體產(chǎn)業(yè)發(fā)展的主要驅(qū)動力,預(yù)計2020年智能手機的出貨量將達(dá)20億部。

目前主要的扇入型封裝器件為WiFi/BT(無線局域網(wǎng)、藍(lán)牙)集成組件、收發(fā)器、PMIC(電源管理集成電路)和DC/DC轉(zhuǎn)換器(約占總量的50%),以及包括MEMS和圖像傳感器在內(nèi)的各種數(shù)字、模擬、混合信號器件。扇入型封裝技術(shù)未來可能面臨的[敏感詞]挑戰(zhàn),或?qū)⑹窍到y(tǒng)級封裝的器件功能集成。下圖為系統(tǒng)級封裝增長對扇入型封裝出貨量的影響,其整體復(fù)合年增長率從9%下降到了6%。本報告詳細(xì)分析了系統(tǒng)級封裝的增長及其對扇入型封裝的影響。

而扇入型的市場,從2015年的統(tǒng)計顯示,看出外包半導(dǎo)體封測占據(jù)了主要的市場份額,其中包括一家IDM廠商(TI,德州儀器)和一家代工廠(TSMC,臺積電)。STATS ChipPAC(新科金朋)被JCET(長電科技)收購后展現(xiàn)出強勁的跨躍發(fā)展。而在設(shè)計端,Qualcomm(高通)和Broadcom(博通)推動了整個扇入型封裝50%的市場。

關(guān)于封裝技術(shù),過去幾年市場大多關(guān)注扇出型晶圓級封裝技術(shù)的發(fā)展。但是,扇入型封裝走出了一條自己的發(fā)展道路和路徑圖,除了進(jìn)一步擴展,它仍能帶來其它類型的創(chuàng)新技術(shù),如六面模具保護(hù)等。本報告提供了兩種扇入型封裝技術(shù)發(fā)展路徑圖的詳細(xì)分析:一種為大規(guī)模批量生產(chǎn)(HVM)路徑圖,另一種為生產(chǎn)就緒路徑圖。路徑圖包括I/O計數(shù)器、L/S、凸點間距、封裝厚度、尺寸等等。此外,本報告還從利用IC技術(shù)節(jié)點和進(jìn)一步前端擴展扇入型IC器件方面分析了扇入型封裝技術(shù)。盡管扇入型封裝技術(shù)的HVM生產(chǎn)路徑的擴展速度慢于扇出型封裝技術(shù),但扇入型封裝技術(shù)有能力達(dá)到大多數(shù)扇出型封裝的擴展條件,具備隨時可提供的生產(chǎn)就緒發(fā)展路徑。

其次談一下扇出型。

扇出型封裝采取拉線出來的方式,成本相對便宜;fan out WLP可以讓多種不同裸晶,做成像WLP制程一般埋進(jìn)去,等于減一層封裝,假設(shè)放置多顆裸晶,等于省了多層封裝,有助于降低客戶成本。此時[敏感詞]會影響IC成本的因素則為裸晶大小。

2013年起,全球各主要封測廠積極擴充FOWLP產(chǎn)能,主要是為了滿足中低價智慧型手機市場,對于成本的嚴(yán)苛要求。FOWLP由于不須使用載板材料,因此可節(jié)省近30%封裝成本,且封裝厚度也更加輕薄,有助于提升晶片商產(chǎn)品競爭力。

麥姆斯咨詢的報告顯示,2016年是扇出型封裝市場的轉(zhuǎn)折點,蘋果和臺積電的加入改變了該技術(shù)的應(yīng)用狀況,可能將使市場開始逐漸接受扇出型封裝技術(shù)。扇出型封裝市場將分化發(fā)展成兩種類型:

- 扇出型封裝“核心”市場,包括基帶、電源管理及射頻收發(fā)器等單芯片應(yīng)用。該市場是扇出型晶圓級封裝解決方案的主要應(yīng)用領(lǐng)域,并將保持穩(wěn)定的增長趨勢。

- 扇出型封裝“高密度”市場,始于蘋果公司APE,包括處理器、存儲器等輸入輸出數(shù)據(jù)量更大的應(yīng)用。該市場具有較大的不確定性,需要新的集成解決方案和高性能扇出型封裝解決方案。但是,該市場具有很大的市場潛力。

由于扇出型封裝技術(shù)具有潛力巨大的“高密度”市場和增長穩(wěn)定的“核心”市場,該領(lǐng)域的供應(yīng)鏈預(yù)計將在扇出型封裝能力方面投入巨資。一些廠商已經(jīng)能夠提供扇出型晶圓級封裝,但還有許多廠商仍處于扇出型封裝平臺的開發(fā)階段,以期能夠進(jìn)入扇出型封裝市場,擴大它們的產(chǎn)品組合。

除了臺積電之外,STATS ChipPAC(新加坡星科金朋)將利用JCET(江蘇長電科技)的支持進(jìn)一步投入扇出型封裝技術(shù)的開發(fā)(2015年初,江蘇長電科技以7.8億美元收購了新加坡星科金朋);ASE(日月光集團)則和Deca Technologies建立了深入的合作關(guān)系(2016年5月,Deca Technologies獲日月光集團6000萬美元投資,日月光集團則獲得Deca Technologies的M系列扇出型晶圓級封裝技術(shù)及工藝授權(quán));Amkor(安靠科技)、 SPIL(矽品科技)及Powertech(力成科技)正瞄準(zhǔn)未來的量產(chǎn)而處于扇出型封裝技術(shù)的開發(fā)階段。三星看上去似乎有些落后,它正在抉擇如何參與競爭。

而在市場容量方面,扇出型封裝保持56%的復(fù)合年增長率,未來將會給封測廠商帶來廣闊的前景。

但這個新技術(shù)在未來還要面臨很大的挑戰(zhàn),Amkor中國區(qū)總裁周曉陽表示,F(xiàn)an-out技術(shù)在尺寸比較小、比較薄,速度比較快的應(yīng)用領(lǐng)域,該技術(shù)會有很大的需求。目前的Fan-out成本相對較高,需要在技術(shù)上進(jìn)一步優(yōu)化。該技術(shù)除了wafer-based之外,還有不少廠商也在做panel-based。

目前,臺積電(TSMC)也是Fan-out技術(shù)的主要推動者之一,而Amkor和其他主要封測公司也都有各自不同形式的Fan-out獨門技術(shù)。相對來講,目前的Fan-out技術(shù)還不是很成熟,其成品率和可靠性還有待于進(jìn)一步提升。

注:本文轉(zhuǎn)載自網(wǎng)絡(luò),支持保護(hù)知識產(chǎn)權(quán),轉(zhuǎn)載請注明原出處及作者,如有侵權(quán)請聯(lián)系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經(jīng)理

QQ:332496225 丘經(jīng)理

地址:深圳市龍華新區(qū)民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2024 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號-1