保守來講,當下8英寸(200mm)晶圓的供應鏈情況相當嚴峻!

然而,這絕不是新問題。中國臺灣的市場調查公司一一TrendForce于2020年11月發布新聞稱:“就8英寸晶圓的產能而言,自2019年下半年以來一直持續在嚴重的供給不足問題”。

此外,雪上加霜的是2021年3月瑞薩電子那珂工廠發生了火災。由于瑞薩的此處工廠為諸多車型供貨,因此導致問題更加惡化。

基于以上背景,導致諸多因素“糾纏”在一起。但是,不言而喻,[敏感詞]的原因還是在于新冠疫情(COVID-19)。由于新冠疫情的發生,耳機、電腦、電視、顯示屏、手機等各種電子產品的需求猛增。

雖然汽車也屬于以上范疇,但人們還是希望汽車市場會在2021年內從新冠疫情的陰影中恢復。如今各種產品都在推廣將多種功能匯集于一體的SoC(System on Chip)模式,因此很多產品都需要搭載多個具備數模混合信號(Mixed Signal Chip)的IC。以上產品的用途方向主要有以下:PMIC(Power Management IC)、CMOS圖像傳感器、指紋識別傳感器、汽車發動機/底盤控制、顯示屏驅動IC、Sub Giga Hertz的無線通信芯片等。一般情況下,以上這些都適用180納米、350納米工藝,用8英寸晶圓生產。

即,用于這種數模混合信號芯片(Mixed Signal Chip)、功率半導體的產品需求不斷增長,這導致了8英寸晶圓的產能不足。

受到8英寸晶圓的供給達到極限的影響,代工廠(Foundry)很有可能會擴大產能。代工廠可能會收購垂直統籌型廠家(IDM:Integrated Device Manufacturer)的8英寸晶圓生產設備和產線。可列舉的事例如下:最近有報道指出,中國臺灣的UMC正在討論收購Japan Semiconductor(原東芝的半導體制造公司) 的8英寸產線。

沒有供生產廠家

正如Trend Force的報道指出的一樣,自2019年下半年開始的嚴重的半導體供給不足問題,可以推測的原因是幾乎沒有廠家可以生產出8英寸晶圓的設備,即使現在也是如此,因此半導體生產設備的價格不斷高漲。

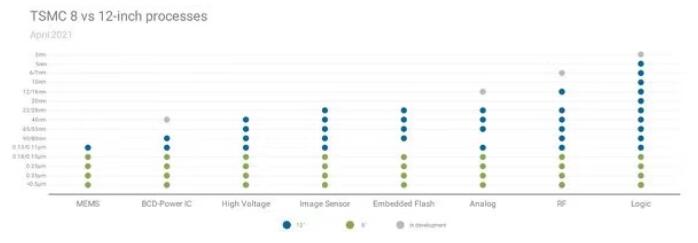

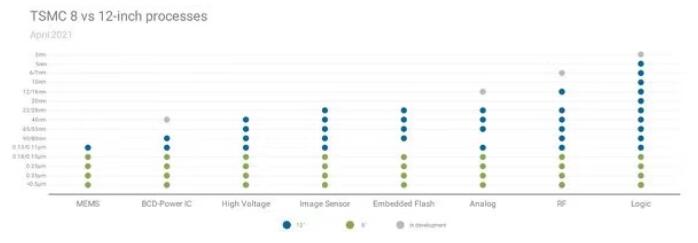

TSMC的采用8英寸、12英寸晶圓的工藝。(圖片出自:eetimes) 此外,8英寸晶圓的價格較12英寸低得多,因此,代工廠普遍認為擴大8英寸產能的成本效率更差。因此,產生了一系列連鎖反應,如一部分代工廠就對客戶提高了8英寸晶圓的價格。

換句話說,就8英寸晶圓的情況而言,與其說“供應鏈混亂”,不如說其特點是“供應廠家不足”。 一部分“移步”12英寸晶圓

就12英寸(300mm)晶圓的代工廠而言,以TSMC、GLOBALFOUNDRIES為代表的各家企業為擴大產能而在火熱地投資,然而,卻看不到任何有關8英寸的改善情況。

由于8英寸晶圓產能沒有任何改善,因此一部分廠家正在從現有的180nm、350nm的8英寸產線轉為使用12英寸晶圓。此外,很多代工廠可以提供用12英寸晶圓生產的130nm工藝,因此可用作二次供給源或者主要供給源。因此,這有助于提高供應鏈的地理多樣性。 180納米、130納米工藝技術的特征

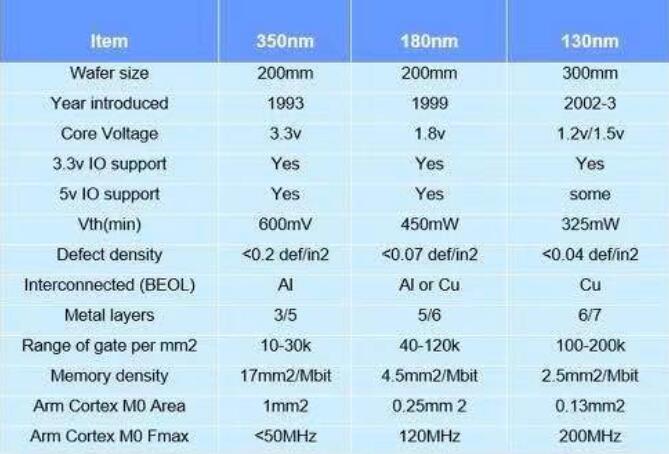

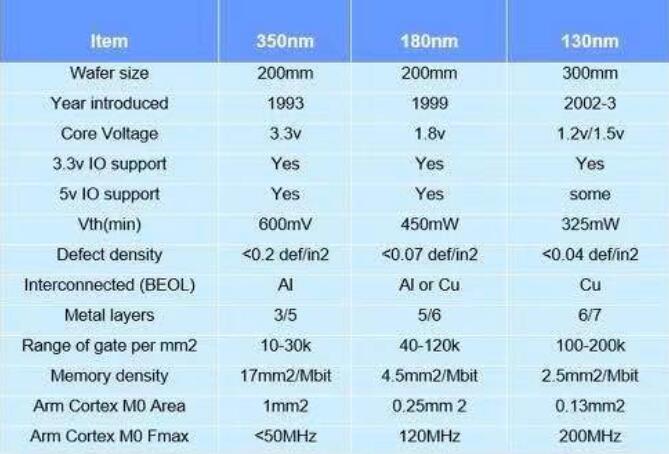

180納米和130納米工藝雖然有類似的工藝,但也有不同的地方。主要是晶體管的閾值電壓的下降程度不同,核心供給電壓為1.8V一1.5V,或者低至1.2V。此外,由于存在各種工藝技術的選擇項,因此可以支持5V/3.3V的IO電壓,就對于模擬/RF設計極其重要的被動零部件而言,這些工藝特征極其類似。

用于Mixed Signal ASIC等產品的主要節點技術比較圖。(圖片出自:eetimes)

12英寸晶圓技術有多個優勢。由于可代替舊代際技術中的鋁而使用銅,因此電流密度允許值也較高,耐電遷移性也較優秀。此外,金屬層的層數也較多,晶體管尺寸較小,因此,通過提高晶體管密度、布線密度,可以縮小芯片尺寸、提高性能。

此外,大部分180納米工藝技術和大部分的130nm BCD(Bipolar-CMOS-DMOS)工藝技術都可以支持STI(Shallow Trench Isolation,淺槽隔離)等功能,因此與大部分在350納米技術中使用的LOCOS(Local Oxidation of Silicon)絕緣相比,因此可以獲得較高的密度、閂鎖效應(Latch Up)保護機能等。因此,達到提高線路性能和穩定性的效果。

如今,130納米 BCD工藝已經相當成熟,因此可作為各種工藝技術的選擇項。如不同級別的高壓晶體管、非揮發性存儲半導體、MIM(金屬一一絕緣膜一一金屬)電容、

穩壓二極管(Zener)/

肖特基二極管等。因此,不僅可以將復雜的模擬/RF功能與SoC解決方案融合,還可以提供其他優勢。 8英寸晶圓還有很多優勢

8英寸晶圓還有很多優勢,比方說,用350納米制造的8英寸晶圓的價格優勢。

原因如下:生產設備已經完成折舊、生產工藝相對簡單(層數少)。此外,一部分模擬線路未必能夠在新工藝中順利實現微縮化,因此與130納米同等程度的半導體芯片的價格可能會高于350納米。但是,當因零部件不足導致無法生產產品時,大部分情況下會發生極其嚴重的情況,而不是單純的半導體芯片的成本差。

此外,現階段人們的關注點是盡管各家代工廠都在從8英寸轉到12英寸,但卻沒有一家廠家做出任何發言。對于Mixed Signal ASIC熟練的廠家雖然在努力,但首先應該著手于線路圖的端口、IC 的數據手冊(Data Sheet)。

就為重新設計ASIC所需的投資而言,應該統籌一下其他產品,以免同樣受到如8英寸供應鏈同樣問題。

130納米的特征尺寸(Feature Size)較小,因此可以在不增加成本的情況下與“Arm Cortex-M”系列核融合。低端CPU所需要的芯片面積僅為數平方毫米,而且有可能以較高的效率與64kbit/128kbit的SRAM融合。

從如今的數據手冊來看,從設計ASIC、量產、獲得認證的日程需要14個月一一24個月(依復雜程度而定),最初的Proto Type Silicon應該可以在一年內完成。如果是車載產品,從制作規格書到PPAP(Production part approval process,生產件批準程序)大概需要24個月一一36個月(依復雜程度而定)。130納米ASIC的一般預算為60萬美元起步(依據實際的復雜程度和IP知識產權內容而定),如果依據AEC-Q100的話,費用為400萬美元左右。如今,130納米工藝(12英寸晶圓)的Mask Tool的成本為20萬美元以下,占整體成本的比例較低。

很多Mixed Signal Device都是由供給不足的8英寸晶圓制造的,由于8英寸晶圓產線的投資不足(原因是投資收益率低下),未來供應鏈問題還會繼續存在。

此次的半導體供給不足問題某種程度上是一個“警告”,如今使用8英寸晶圓的企業應該首先考慮一下未來的需求。此外,無論是主要生產據點,還是第二供應商(Second Source),在所有的工藝完成之前都需要確保足夠的時間。

免責聲明:本文轉載自“半導體行業觀察”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室