2月18日至22日,2024年國際固態電路會議(ISSCC’24)在美國舊金山召開。清華大學集成電路學院王志華教授和池保勇教授牽頭的“低功耗、射頻集成電路與醫療微電子”團隊在ISSCC’24上發表了3篇學術論文,研究內容涵蓋量子計算芯片、頻率源芯片、鎖相環時基芯片等。自2008年始,團隊已在ISSCC上累計發表論文16篇。

ISSCC (International Solid-State Circuits Conference,國際固態電路會議)始于1953年,是全球學術界和工業界公認的集成電路設計領域[敏感詞]級別會議,被認為是“集成電路設計領域的奧林匹克大會”。ISSCC通常是各個時期國際上最[敏感詞]固態電路技術最先發表之地。每年吸引超過3000名來自世界各地工業界和學術界的參會者。2024年ISSCC共錄用同行評審論文234篇。

01

極低功耗雙量子比特接口芯片組

極低功耗雙量子比特接口芯片組及測試環境

隨著規模化量子計算研究的不斷深入,可在超低溫環境下有效工作的量子比特操控與讀出芯片被認為是實現規模化實用量子計算機的關鍵支撐技術。該項技術的核心挑戰是在有限的制冷功率條件下提升量子比特接口芯片的可操控和讀出通道數,推動實現量子比特的大規模集成。為攻克這一技術難題,推進量子計算機小型化和集成度,研究并突破超低功耗的量子比特接口芯片設計技術具有重大意義。研究團隊在前期CMOS工藝超低溫特性建模、高集成度量子比特控制芯片等研究基礎之上,設計出極低功耗的雙量子比特接口芯片組(含完整操控與讀出)。該芯片組基于相位域信號處理的極化調制和反射讀出技術,在3.5K低溫環境下可以產生雙超導量子比特控制、讀出所需的XY通道任意包絡脈沖信號、Z通道偏置信號和反射讀出激勵信號,實現了基于相位信息的量子比特狀態檢測電路,同時片上集成了時鐘產生、指令存儲等電路,芯片組功耗相對于國際上同類研究大幅降低。該芯片在北京量子信息科學研究院量子計算云平臺實現了對超導量子比特的有效控制及狀態讀出。該工作以“A Cryo-CMOS Quantum Computing Unit Interface Chipset in 28nm Bulk CMOS with Phase-Detection based Readout and Phase-Shifter based Pulse Generation”為題發表在ISSCC‘24。論文[敏感詞]作者為郭衍束博士,團隊的姜漢鈞副教授、李鐵夫副研究員為該項研究工作的主要負責人。

02

多模多核超寬帶射頻壓控振蕩器

所提出“模式分裂”技術的工作原理以及基于此技術的多模多核VCO的電路原理圖

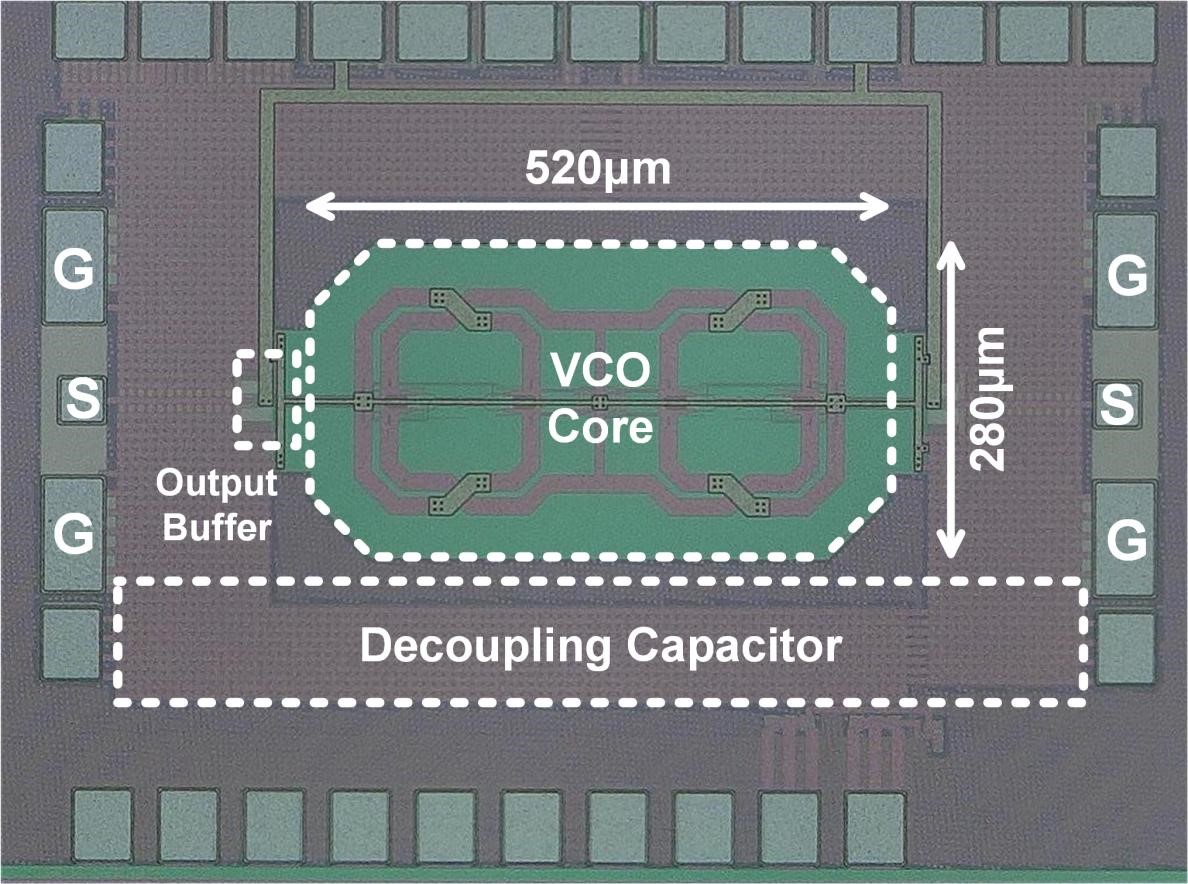

所設計的超寬帶壓控振蕩器的顯微照片

應用于射頻收發前端的寬帶毫米波頻段的本地振蕩器對于5G通信技術的毫米波應用以及高性能雷達技術有著重要意義。目前文獻中所報導的高性能振蕩[敏感詞]多帶寬有限,無法應用于寬帶的通信系統中;同時,既有的寬帶振蕩器又存在相位噪聲隨帶寬增加而惡化嚴重的問題。以此為出發點,研究團隊提出了一種基于“模式分裂”技術的多模多核超寬帶射頻壓控振蕩器。該技術在傳統的雙核雙模的“8”字型電感拓撲結構的基礎上,通過引入一對對稱的輔助諧振腔與主諧振腔產生同相或反相磁場耦合,不僅產生了四種等效電感,從而將原有的兩種模式分裂成了四種模式,極大地擴展了振蕩器的帶寬,而且在不增加面積的情況下額外引入了兩個核心,相比于傳統的單核結構降低了6dB的相位噪聲。所提出的多模多核寬帶振蕩器可以覆蓋13.7至41.5GHz的基頻范圍,即101%的分數帶寬,同時在10MHz處頻偏處的峰值FoM及FoMT分別達到了194.0至214.1dBc/Hz。值得說明的是,該芯片是[敏感詞]顆同時達到100%以上分數帶寬及高于210dBc/Hz FoMT的寬帶振蕩器,具有[敏感詞]的性能。該工作以“A 13.7-to-41.5GHz 214.1dBc/Hz FoMT Quad-Core Quad-Mode VCO Using an Oscillation-Mode-Splitting Technique”為題發表在ISSCC’24。集成電路學院本科生葛桓羽為論文[敏感詞]作者,團隊的賈海昆副教授為論文通訊作者。

03

超低電壓混合型分數鎖相環

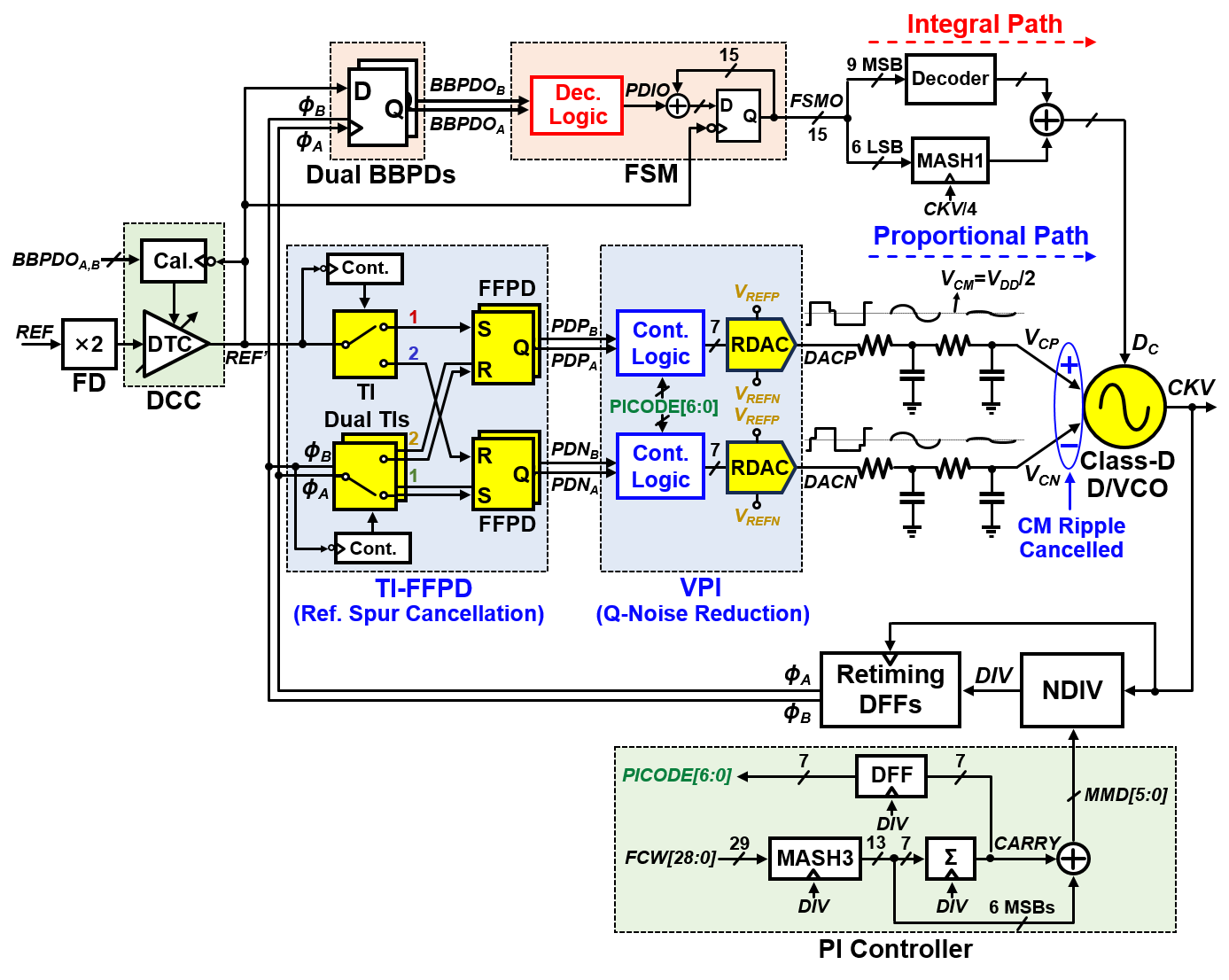

基于電壓模相位插值器的超低電壓混合型分數鎖相環架構

鎖相環芯片顯微照片

低電壓鎖相環對實現低功耗數字系統的動態電壓調整以及物聯網設備的無線能量收集供電具有重要的意義。整數型鎖相環芯片已經可以實現低于0.4V的電源電壓,但是,由于傳統的鑒相器和量化噪聲消除方法的性能在低電壓下受到嚴重影響,目前報道的[敏感詞]供電電壓的CMOS分數型鎖相環采用0.5V電壓供電,且需要內置升壓模塊。針對以上問題,研究團隊提出了一種基于電壓模的相位插值器,該方法通過一個電阻型數模轉換器(RDAC)在電壓域實現量化噪聲補償。由于其量化精度依賴于無源元器件(電阻)的比例,其在0.5V電源電壓并考慮PVT變化的條件下實現了<0.15 LSB的線性度,且無需進行增益和線性度的校準。基于該電壓模相位插值器以及時鐘交織的觸發器型鑒相器(TI-FFPD),團隊在28nm CMOS工藝下實現了一款工作在2.4GHz的無偏置電流的混合型分數鎖相環。該鎖相環在0.45V電壓下實現了小于600fs的積分抖動以及-57dBc的最差雜散,功耗為0.72mW,且無內置升壓模塊。該工作以“A 0.45V 0.72mW 2.4GHz Bias-Current-Free Fractional-N Hybrid PLL Using a Voltage-Mode Phase Interpolator in 28nm CMOS”為題發表在ISSCC’24。集成電路學院博士研究生馮禮群為論文[敏感詞]作者,團隊的李宇根教授為論文通訊作者。