服務熱線

0755-83044319

發布時間:2022-03-17作者來源:薩科微瀏覽:3789

1:摩爾定律

1965年,硅谷傳奇,仙童“八叛徒”之一,英特爾原首席執行官和榮譽主席,偉大的規律發現者戈登·摩爾正在準備一個關于計算機存儲器發展趨勢的報告。

在他開始繪制數據時,發現了一個驚人的趨勢。

每個新的芯片大體上包含其前任兩倍的容量,每個芯片產生的時間都是在前一個芯片產生后的18~24個月內,如果這個趨勢繼續,計算能力相對于時間周期將呈指數式的上升。

這個就是大名鼎鼎的摩爾定律, 其對集成電路產業的發展描述,異乎尋常的正確。

總結來說:

1:集成電路芯片(wafer)上所集成的電路的數目,每隔18個月就翻一番。

2、微處理器的性能每隔18個月提高一倍,而價格下降一半。

3、用一美元所能買到的計算機性能,每隔18個月翻兩番。

你可能覺得摩爾定律平平無奇,只不過是一個總結?

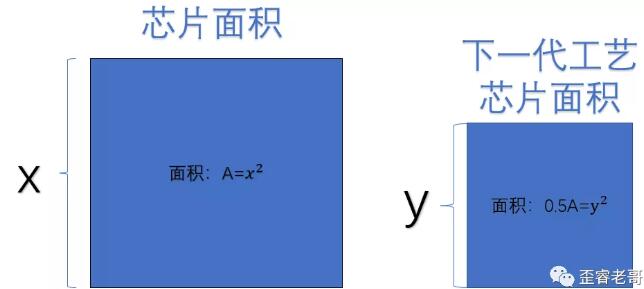

其實這可以推導出了一個公式,那就是每18個月,在芯片規模不變的情況下,芯片面積減半。

這樣相同的大小的wafer,可以生產出多一倍的芯片。

如果上一代工藝芯片面積是1mm2,在新工藝上,面積就是新工藝的一半,也就是0.5mm2。

我們假設兩代工藝wafer成本一樣(一般新工藝會貴一些),那么采用新工藝,其成本是原來工藝成本的一半。

這個就是摩爾定律揭示的現實:

那就是,采用新工藝的芯片,面積更小,功耗更優,頻率更高,成本還更低。

這個就是新工藝對老工藝降維式的打擊!

這些優點和好處就是驅動芯片工藝不斷進步的發動機。

也就是摩爾定律的內涵。

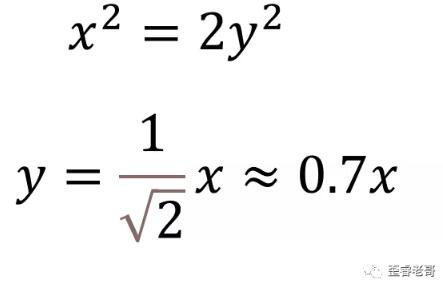

那如果芯片工藝進步,每個晶體管的尺寸就會縮小,那到底縮小多少?

如上圖所示,晶體管數量保持不變的情況下, 下一代新工藝的芯片面積是上一代的一半。

那么X和Y什么關系。

如果我們按照正方形來計算的話?

那么新工藝大約是老工藝晶體管尺寸的0.7倍。

也就是晶體管會縮小0.7倍。

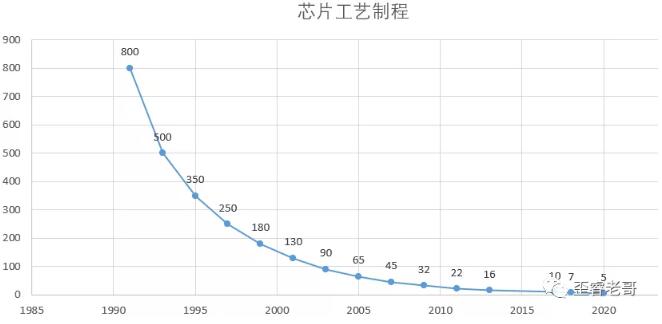

那根據摩爾定律,我們利用初中數學知識,就能算出每一代工藝的進步,從800nm開始(這個80586的工藝節點)。

而芯片工藝的發展也印證了這一點:

從0.8 μ m、0.5 μ m、0.35 μ m、0.25 μ m、0 .18 μm、0.13 μ m、90nm、65nm、45nm、32nm、22nm、16nm、10nm、7nm,5nm。

實際的工藝節點,符合了這個要求。

摩爾定律和現在芯片制程完全吻合。

神奇!

2:半節點

可能有些工藝制程知識的同學會說:

有點不對勁,

這個圖里,制程很火的40nm,28nm,14nm跑哪里去了。

對,這就涉及到一個芯片制造廠常用的手段。

shrink。

我們都知道,一個工藝節點研發成功后,其研發成本是很高的。

如果可以在這個工藝節點上持續優化,面積,功耗等等。

也是一種[敏感詞]化利用原有投入的方式。

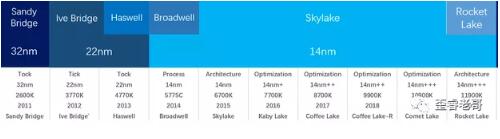

就像intel就在14nm上做的一樣。

14nm+++

持續優化。

而我們今天講的shrink,也是一種優化。

它本質上是利用光照(MASK)等比例縮放后。晶體管尺寸縮小一點,芯片仍然能夠正常工作,從而減少芯片面積,降低成本。

那么shrink的比例是多少?

Shrink 一般可以將晶體管的尺寸縮小0.9倍。

大約每個邊長縮放為0.9;整體面積縮小0.81;

這個過程又稱為,芯片收縮(die shrink)。

然而,按比例縮小可能引入新的問題,例如漏電流增大,但是通過工藝參數可以來調節漏電,shrink在不改變工藝特性的基礎上,修修補補,也能挖掘這個工藝節點的潛力。

這些shrink后的工藝節點,也被人稱為半節點。

例如:

40nm是45nm shrink后的半節點。

28nm是32nm shrink后的半節點。

20nm是22nm shrink后的半節點。

14nm也可以看作16nm shrink后的半節點。

把前面的工藝,乘以0.9就可以了。

DIE shrink是芯片制造廠家來做的,和芯片設計公司沒有關系。

工程師設計完成的版圖都是 pre shrink的,而到了廠家生產的時候,直接進行shrink,生成的die的面積比版本等比例縮小。

所以我們現在芯片設計工程師,做40nm或者28nm等半節點工藝時,都有一個shrink的流程。

會發現,芯片的版圖比實際的DIE的面積要大。

如果我們計算最后的DIE(芯片)面積,實際上要算shrink之后的,而不是版圖的面積。

EDA工具標注的都是shrink前(pre shrink)的面積。

那就是設計公司給了芯片制造廠一張10X10的設計圖紙,而芯片廠生產的尺寸卻是9x9。

具體DIE,WAFER等定義,不熟悉的同學,可以參見老哥原來寫的的《人類高質量芯片工程師的那些“黑話”》

這些優化后的,40nm,28nm等等,成為了更成熟和長壽的工藝。

而原有的45nm,32nm等,與優化后的40nm,28nm相比,不再具有優勢,廠家不再推這些工藝工藝。

事實上,業界通常把45nm/40nm, 32nm/28nm, 22nm/20nm, 16nm/14nm 這些工藝節點,看作同一個工藝節點,是一代,只是廠家通過shrink這種手段,進行的優化。

加上shrink以后,我們看到目前的28nm,14nm,10nm,7nm,5nm都可以用摩爾定律上一節的初中數學知識算出來。

嚴絲合縫,理論和實際吻合的很好。

戈登.摩爾,真神人也!

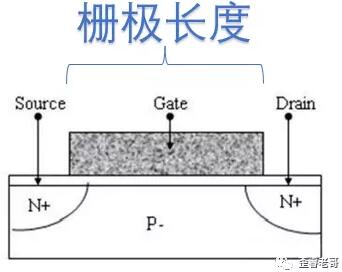

3:柵極長度

但是,事實果真如此嗎?

這些數字里面隱藏著一個極大的隱情。

我們來看一張圖:

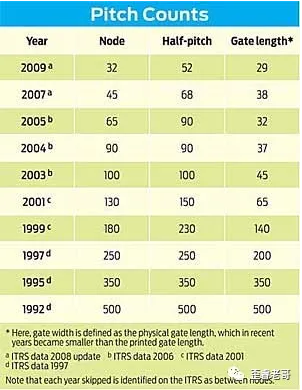

大約從20世紀60年代到90年代末,節點的命名是基于它們的柵極長度命名的。IEEE的此圖表顯示了以下關系。

柵極長度(gate length)和半節距(芯片上兩個相同特征之間的距離的一半)匹配工藝節點名稱,這個其實0.5um,0.35um,0.25um的一些命名的原因。

但是在28nm以下,由于采用finfet這些新的技術,這些和實際的節點和柵極長度,以及半節距(half-pitch)就匹配不上了

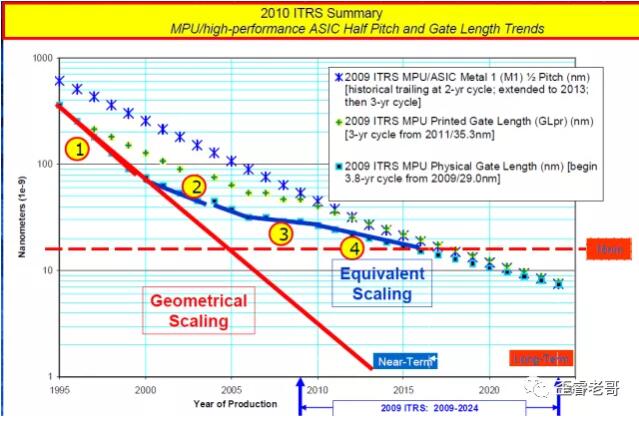

如果保持節點名稱和實際特征尺寸同步,就會如紅線所示。

2015年前,芯片制造的最小工藝尺寸就會跌破1nm。

而實際上,廠家暗渡陳倉了,

而實際上,整個工藝曲線更接近藍線所示。

你以為的7nm,5nm,早已不是原來指的柵極長度(gate length),或者(half-pitch)半節距。

那這個7nm,5nm怎么來的。

畫大餅來的!

畫大餅,這個你是不是比較熟。

公司的老板最擅長搞這個,畫大餅,或者叫畫路線圖(roadmap)。

老板說:未來三年每年增長一倍,今年銷售額1億,10年后就成為銷售千億公司。

關鍵是,這玩意不能這么算,按照這么算,幾十年后,地球都成為你們公司的,你們銷售額也完不成。

那么芯片制造的大餅,或者(roadmap)是怎么畫出來的?

由于半導體制造涉及巨大的資本支出和大量的長期研究。從論文中引入新技術方法到大規模商業制造的平均時間約為10-15年。

幾十年前,半導體行業認識到,如果有一個節點介紹的總體路線圖以及這些節點將針對的功能尺寸,這將對參與芯片流程的每個單位都用導引作用。

也就是說,比如,2025年,我們畫個大餅要搞1nm,那么,這個時候所需要光刻設備廠家,刻蝕設備廠家,材料廠家,研究機構等等,都要瞄準這個目標來做。

這個路線圖,主要是“為大學、財團和行業研究人員提供未來的主要參考,以刺激各個技術領域的創新”。

也就是說,要給芯片制造從業者畫一個大餅。

多年來,國際半導體技術路線圖(ITRS)發布了該行業的總體路線圖。這些路線圖延續了15年,為半導體市場設定了總體目標。

ITRS就是畫大餅的人!

那如何畫這個大餅(roadmap)?

當然是摩爾定律,也就是本文[敏感詞]部分介紹的那樣。

摩爾定律這個就是這么粗暴。

一直從幾百nm,干到5nm或者3nm。

關鍵是,數學可以這么算,物理能這么搞嗎?

這么搞,是不是有點太草率了。

4:營銷手段:寶馬5系和5nm

不久之后, ITRS(國際半導體技術路線圖)這個組織也明白了,這么搞是不行的。

不能把柵極長度(gate length)或半節距(half-pitch)與節點大小聯系起來的原因是:

因此這些尺寸要么停止縮放,要么縮放得更慢了。

粗暴的乘以0.7還能指望晶體管能工作。

這種晶體管,工業界制造不出來。

于是,在2010年,ITRS將每個節點上的技術,統稱為“等效縮放”。

也就是說,不用實際對應上,你覺得差不過就行。

也就是說,7nm,5nm,早已不是原來指的柵極長度(gate length),或者(half-pitch)半節距。

這種改變,反應了芯片制造業的現狀:

臺積電的Philip Wong在Hot Chips 31主旨演講中說:“它過去是技術節點,節點編號,意味著一些東西,晶圓上的一些功能。”。

但是:“今天,這些數字只是數字。它們就像汽車模型——就像寶馬5系或馬自達6。數字是什么并不重要,它只是下一項技術的目的地,它的名稱。因此,我們不要把節點的名稱與技術實際提供的相混淆。”

畫重點:不要把節點的名稱和技術實際相混淆

5nm,7nm這些和寶馬5,馬自達6沒有什么區別。

這些只是營銷的手段而已。

不是大眾要把這個名字相混淆。

而是這些芯片制造廠商,搞這些營銷詞匯,不就是想混淆工藝制程的節點和晶體管的實際尺寸嗎?

雖然摩爾定律這艘大船進入淺水區,快擱淺了。

讓我們一起晃動這艘大船,假裝摩爾定律啟示的那樣繼續前進,

所以英特爾就有人提出來了。

不要扯,5nm,7nm了,直接比拼一下單位面積晶體管的數量好了。

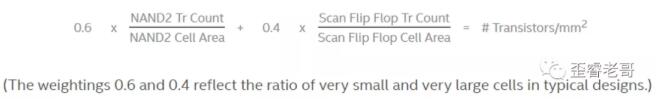

下面就是這個公式:

英特爾的芯片制造專家Mark Bohr提出來的, 它認為每個芯片制造商在提及工藝節點時,都應披露其邏輯晶體管密度,單位為MTr/mm2(每平方毫米數百萬個晶體管)

這個也就是解釋了,為什么英特爾的10nm和臺積電的7nm,雖然看起來是兩代,但是二者的晶體管密度基本一樣。

但是,這個公式太復雜了。

怎么可能有7nm,5nm對大眾的宣傳效果好。

但是,實話實說,英特爾本身自己在命名方案里面,也沒有真正遵循柵極長度(gate length)的模型。

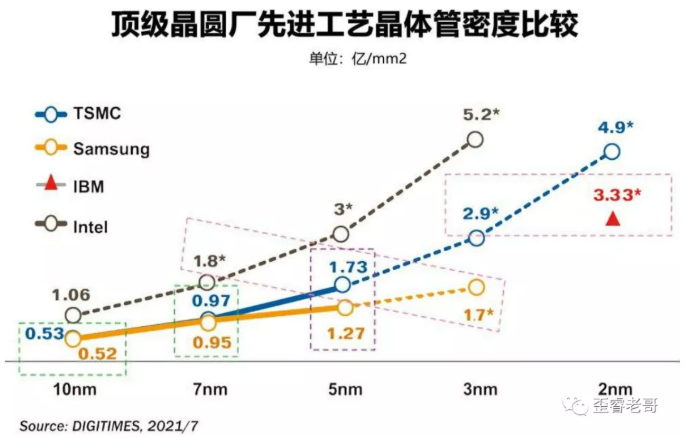

從下表來看,隨著工藝的進步,玩家越來越少了。

高端玩家就剩下了臺積電和三星,還有一直要追趕的英特爾。

明年,三星和臺積電的3nm都號稱要量產。

但是這一次,我們應該知道,這個只是一代工藝代號而已,和3nm本身沒有太大的關系了。

從7nm,5nm,到3nm。

摩爾定律不死。

只是,

步履蹣跚,垂垂老矣。

引用文獻:

1:Technology Node - WikiChip

2:How Are Process Nodes Defined? - ExtremeTech

3: TSMC’s 7nm, 5nm, and 3nm “are just numbers… it doesn’t matter what the number is” | PCGamesN

免責聲明:本文轉載自“路科驗證”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1