服務熱線

0755-83044319

發布時間:2023-02-20作者來源:薩科微瀏覽:2824

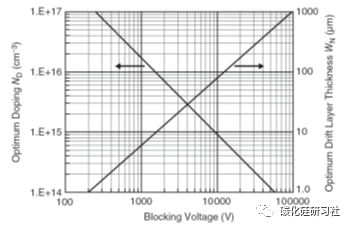

外延層是在晶圓的基礎上,經過外延工藝生長出特定單晶薄膜,襯底晶圓和外延薄膜合稱外延片。其中在導電型碳化硅襯底上生長碳化硅外延層制得碳化硅同質外延片,可進一步制成肖特基二極管、MOSFET、 IGBT 等功率器件,其中應用最多的是4H-SiC 型襯底。

由于碳化硅功率器件與傳統硅功率器件制作工藝不同,不能直接制作在碳化硅單晶材料上,必須在導通型單晶襯底上額外生長高質量的外延材料,并在外延層上制造各類器件,所以外延的質量對器件的性能是影響非常大。不同的功率器,它的性能的提高也對外延層的厚度、摻雜濃度以及缺陷提出了更高要求。

圖1.單極型器件外延層的摻雜濃度和厚度

與阻斷電壓關系曲線

碳化硅外延層的制備方法主要有:蒸發生長法;液相外延生長(LPE);分子束外延生長(MBE);化學氣相沉積(CVD)。這里對這幾種制備方法做了一個基本的總結,見表1。化學氣相沉積(CVD)法是目前工廠大批量生產用的主要方法。

|

|

|

|

|

液相外延生長 (LPE)

|

|

很難控制好外延層的表面形貌。設備不能同時外延多片晶圓,限制了批量生產。 |

|

分子束外延生長(MBE)

|

可以在低生長溫度下生長不同的 SiC 晶型外延層 |

設備真空要求度很高,成本高昂。生長外延層速率慢 |

|

化學氣相沉積(CVD) |

工廠批量生產最主要的方法。生長厚外延層時能夠對生長速率精確控制 |

SiC 外延層仍然存在各種缺陷,從而對器件特性造成影響,所以針對 SiC 的外延生長工藝需要進行不斷的優化 |

|

蒸發生長法

|

使用和SiC拉晶同樣的設備,工藝和拉晶稍微有區別。設備成熟,成本低 |

SiC 的蒸發不均勻,很難利用其蒸發生長出較高質量的外延層 |

表1. 外延層主要制備方法的比較

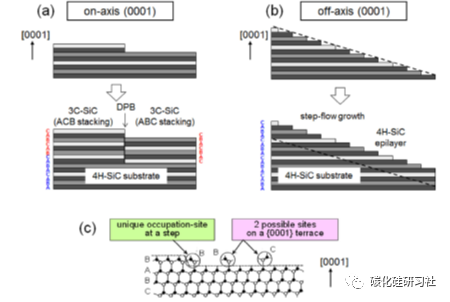

在有一定傾斜角度的偏軸{0001}襯底上,如圖2(b)示意圖,臺階面的密度很大而且臺階面很小,晶體成核不容易在臺階面上發生,多發生在臺階的并入點出,這里只存在一種成核鍵位。所以外延層可以完美地復制襯底的堆垛次序,消除多型體共存的問題。

圖2. 4H-SiC臺階控制外延法的物理過程示意圖

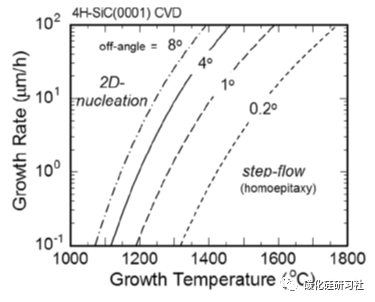

圖3. 4H-SiC臺階控制外延法CVD生長臨界條件

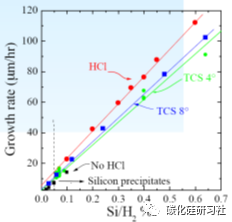

圖4. 4H-SiC外延中不同硅源下的生長速率比較

目前在中低壓應用領域(比如1200伏器件),碳化硅外延的技術相對成熟。它的厚度均勻性、摻雜濃度均勻性以及缺陷分布可以做到相對較優的水平,基本可以滿足中低壓 SBD、MOS、JBS 等器件需求。

但在高壓領域,目前外延片需要攻克的難關還很多。比如10000伏的器件需要的外延層厚度為100μm左右,該外延層的厚度和摻雜濃度均勻性比低壓器件的外延層差很多,尤其是摻雜濃度的均勻性,同時它的三角缺陷也破壞了器件的整體性能。在高壓應用領域,器件的類型趨向于使用雙極器件,對外延層的的少子壽命要求比較高,也需要優化工藝來提高少子壽命。

當前國內外延主要以 4 英寸和 6 英寸為主,大尺寸碳化硅外延片占比逐年遞增。碳化硅外延尺寸主要受制于碳化硅襯底尺寸,當前 6 英寸碳化硅襯底已經實現商用,因此碳化硅襯底外延也逐漸從 4 英寸向 6 英寸過渡。

隨著碳化硅襯底制備技術的提升及產能擴張,碳化硅襯底價格正在逐步降低。在外延片價格構成中,襯底占據了外延 50%以上的成本,隨著襯底價格的下降,碳化硅外延價格也有望降低。

免責聲明:本文采摘自網絡,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1