服務熱線

0755-83044319

發布時間:2022-03-18作者來源:薩科微瀏覽:2052

上接最強的芯片產業鏈科普,芯片自主可控深度解析(一)

刻蝕機

刻蝕是將晶圓表面不必要的材質去除的過程。刻蝕工藝位于光刻之后。

光刻機用光將掩膜上的電路結構復制到硅片上,刻蝕機把復制到硅片上的電路結構進行微雕,雕刻出溝槽和接觸點,讓線路能夠放進去。

按照刻蝕工藝分為干法刻蝕以及濕法刻蝕,干法刻蝕主要利用反應氣體與等離子體進行刻蝕,濕法刻蝕工藝主要是將刻蝕材料浸泡在腐蝕液內進行刻蝕。

干法刻蝕在半導體刻蝕中占據主流,市場占比達到95%,其[敏感詞]優勢在于能夠實現各向異性刻蝕,即刻蝕時可控制僅垂直方向的材料被刻蝕,而不影響橫向材料,從而保證細小圖形保真性。濕法刻蝕由于刻蝕方向的不可控性,在先進制程很容易降低線寬,甚至破壞線路本身,導致芯片品質變差。

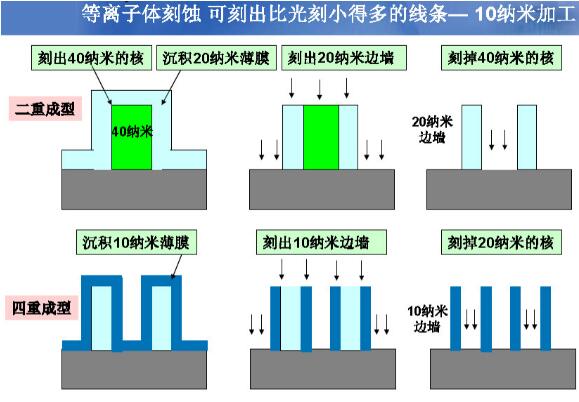

目前普遍采用多重模板工藝原理,即通過多次沉積、刻蝕工藝實現需要的特征尺寸,例如14nm制程所需使用的刻蝕步驟達到64次,較 28nm提升60%;7nm制程所需刻蝕步驟更是高達140次,較14nm提升118%。

下圖所示為多次刻蝕原理。

和光刻機一樣,刻蝕機的廠商也相對較少,代表企業主要是美國的 Lam Research(泛林半導體)、AMAT(應用材料)、日本的TEL(東京電子)等企業。這三家企業占據全球半導體刻蝕機的94%的市場份額,而其他參與者合計僅占6%。其中,Lam Research 占比高達55%,為行業龍頭,東京電子與應用材料分別占比20%和19%。

國內的情況,目前刻蝕設備代表公司為中微公司、北方華創等。中微公司較為領先,工藝節點已經達到5nm。在全球前十大晶圓企業中,中微公司已經進入其中六家,作為臺積電的合作伙伴協同驗證14nm/7nm/5nm等先進工藝。

基于此,如果目前在光刻機領域我們還無力做出改變,那么已經有一定優勢的刻蝕機勢必會成為國產替代的先鋒。

2.2 工藝制程

芯片制造過程需要兩千多道工藝制程,下面,我們按照8大步驟對芯片制造工藝進行簡單介紹。

1. 光刻(光學顯影)

光刻是經過曝光和顯影程序,把光罩上的圖形轉換到光刻膠下面的晶圓上。光刻主要包含感光膠涂布、烘烤、光罩對準、 曝光和顯影等程序。曝光方式包括:紫外線、極紫外光、X射線、電子束等。

2. 刻蝕(蝕刻)

刻蝕是將材料使用化學反應或物理撞擊作用而移除的技術。干刻蝕(dry etching)利用等離子體撞擊晶片表面所產生的物理作用,或等離子體與晶片表面原子間的化學反應,或者兩者的復合作用。濕刻蝕(wet etching)使用的是化學溶液,經過化學反應達到刻蝕的目的。

3. 化學氣相沉積(CVD)

CVD利用熱能、放電或紫外光照射等化學反應的方式,將反應物在晶圓表面沉積形成穩定固態薄膜(film)的一種沉積技術。CVD技術在芯片制程中運用極為廣泛,如介電材料(dielectrics)、導體或半導體等材料都能用CVD技術完成。

4. 物理氣相沉積(PVD)

PVD是物理制程而非化學制程,一般使用氬等氣體,在真空中將氬離子加速以撞擊濺鍍靶材后,可將靶材原子一個個濺擊出來,并使被濺擊出來的材質如雪片般沉積在晶圓表面。

5. 離子植入(Ion Implant)

離子植入可將摻雜物以離子型態植入半導體組件的特定區域上,以獲得精確的電特性。離子先被加速至足夠能量與速度,以穿透(植入)薄膜,到達預定的植入深度。離子植入可對植入區內的摻質濃度加以精密控制。

6. 化學機械研磨(CMP)

化學機械研磨技術具有研磨性物質的機械式研磨與酸堿溶液的化學式研磨兩種作用,可以使晶圓表面達到全面性的平坦化,以利后續薄膜沉積。

7. 清洗

清洗的目的是去除金屬雜質、有機物污染、微塵與自然氧化物;降低表面粗糙度;幾乎所有制程前后都需要清洗。

8. 晶片切割(Die Saw)

晶片切割是將加工完成的晶圓上一顆顆晶粒裸芯片(die)切割分離,便于后續封裝測試。

2.3 材料

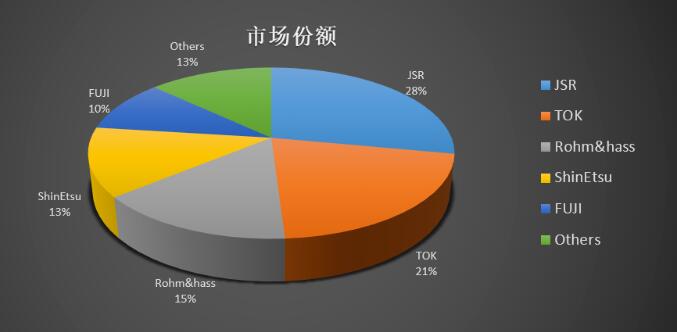

高分辨率的半導體光刻膠是半導體化學品中技術壁壘[敏感詞]的材料,日美企業技術領先國內企業二十年至三十年。 從光刻膠技術水平來看,國內企業在缺乏經驗、缺乏專業技術人才、缺失關鍵上游原材料和設備的條件下,探索出一條自主研發之路,光刻膠高端技術短期內尚難突破,還要很長的路要走。在PCB領域,國產光刻膠具備了一定的量產能力,已經實現對主流廠商供貨。

高分辨率的半導體光刻膠是半導體化學品中技術壁壘[敏感詞]的材料,日美企業技術領先國內企業二十年至三十年。 從光刻膠技術水平來看,國內企業在缺乏經驗、缺乏專業技術人才、缺失關鍵上游原材料和設備的條件下,探索出一條自主研發之路,光刻膠高端技術短期內尚難突破,還要很長的路要走。在PCB領域,國產光刻膠具備了一定的量產能力,已經實現對主流廠商供貨。

03

封 裝 測 試

3.1 芯片封裝

我們從封裝設計和產品封裝兩方面來分析芯片封裝。

早先的封裝中沒有集成(Integration)的概念,封裝設計是比較簡單的,對工具要求也很低,Auto CAD就是常用的封裝設計工具,隨著MCM、SiP技術的出現,封裝設計變得越來越復雜,加上目前SiP、先進封裝、Chiplet、異構集成概念的市場接受度越來越高,封裝內集成的復雜度和靈活度急劇上升,對封裝設計的要求也越來越高,

SiP和先進封裝設計工具目前只有Cadence和 Siemens EDA(Mentor)兩家,Cadence是老牌的封裝設計EDA提供商,市場占有率高,用戶的忠誠度也比較高。

Siemens EDA(Mentor)是封裝設計領域的后起之秀,但其技術先進性上則體現了“后浪”的特點。業界大佬TSMC, Intel, SAMSUNG紛紛選擇Siemens EDA作為其先進封裝(HDAP)的[敏感詞]工具,主要在于兩點:先進的設計工具和強悍的驗證工具。

首先我們說說設計工具,在一次技術論壇中,我說:“不同于傳統封裝設計,先進封裝和SiP設計對3D環境要求很高,3D設計環境不在于是否看上去很直觀、絢麗,而在于對客觀元素的精準描述,包括鍵合線、腔體、芯片堆疊、硅轉接板、2.5D集成、3D集成,Bump...”

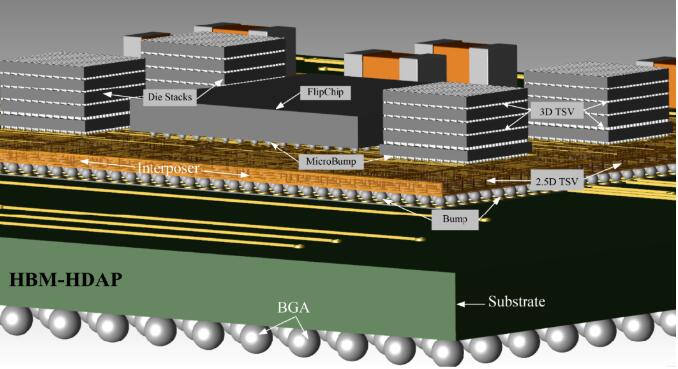

在這一點上,Siemens EDA的SiP及先進封裝設計工具已經遠遠將其競爭對手拋在身后。下圖為先進封裝版圖設計工具XPD中的封裝設計3D截圖,4組芯片堆疊中,每組5顆芯片(4HBM+1Logic)以3D TSV連接在一起,和GPU一起集成在硅轉接板(2.5D TSV)上,硅轉接板和電阻、電容等一起集成在封裝基板上。

XPD中的先進封裝設計截圖(3D)

該設計中包含了3D集成、2.5D集成、倒裝焊、Bump、多基板集成等多種方式,在XPD設計環境中得到了精準的實現。 先進封裝驗證工具包括電氣驗證和物理驗證,電氣驗證包含80多條規則,對整個系統進行信號完整性、電源完整性、EMI\EMC等電氣相關的檢查和驗證,物理驗證則是基于IC驗證工具Calibre,整合出Calibre 3D STACK,專門用于3D先進封裝的物理驗證。 隨著封裝內的集成度、設計復雜度越來越高,對工具的要求也越來越高,另外,在先進封裝領域,封裝設計和芯片設計的協同度日益提高,在某種程度上有逐漸融合的趨勢,因此對協同設計的要求也日益提升。 關于SiP、微系統、先進封裝的詳細設計方法和實際案例,可參考電子工業出版社近期即將出版的新書: 《基于SiP技術的微系統》

3.2 芯片測試

機臺測試

測試向量可基于EDA工具的仿真向量(包含輸入信號和期望的輸出),經過優化和轉換,形成ATE格式的測試向量。利用EDA工具建立器件模型,通過建立一個Testbench仿真驗證平臺,對其提供測試激勵,進行仿真,驗證結果,將輸入激勵和輸出響應存儲,按照ATE向量格式,生成ATE向量文件。

系統測試

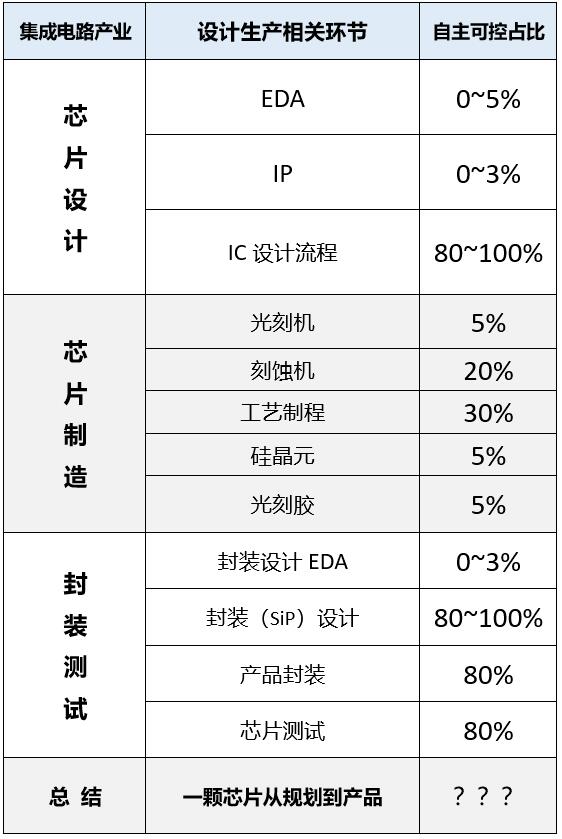

自主可控總結

只有真正認識到自身的不足,實事求是,踏踏實實,一步一個腳印,并持之以恒,才能在激烈的競爭中不致落后,從而減少卡脖子事件的發生!

免責聲明:本文轉載自“芯論語”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1