服務熱線

0755-83044319

發(fā)布時間:2022-03-18作者來源:薩科微瀏覽:2010

近日,拜讀遼寧工業(yè)大學陳永真教授的文章“氮化鎵FET用電解電容器只不過是噱頭?”感觸良多,應運而生的氮化鎵(GaN)FET(場效應晶體管)用電解電容器除了體積減小,在制造工藝沒有本質性改變時,其寄生電感無法大幅降低,且在高開關頻率下已呈電感特性,高次諧波頗豐。所以,這樣的電解電容器不用也罷。

的確,在新一代創(chuàng)新技術迭代時刻,總是會泥沙俱下。不過,瑕不掩瑜,隨著新技術周邊配套工藝技術的進展,其作用也將越來越大,氮化鎵功率器件就是這樣。我們看看近來業(yè)界大咖們對于氮化鎵又有哪些高論,能給我們哪些方面的借鑒?

GaN已成為5G能量催化劑

“氮化鎵的出現將滿足5G需求,實現新的拓撲結構,并徹底改變快速充電,”Navitas Semiconductor企業(yè)營銷和投資者關系副總裁Stephen Oliver如是說。

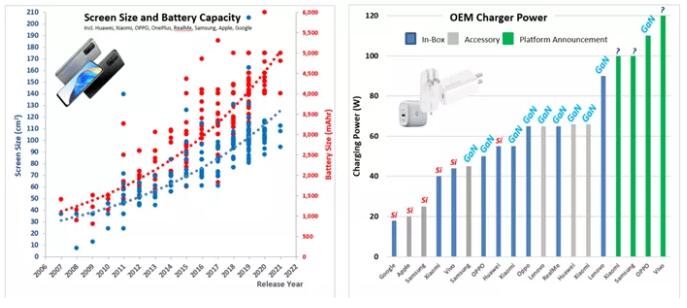

GSMArena發(fā)布的數據表明,自2010年以來,蘋果iPhone 12、小米Mi11和三星S21等新手機平臺的平均屏幕尺寸和電池容量增加了3倍以上。使用速度慢的硅基5W或20W商用充電器的充電時間延長已令人不可接受,所以需要更大的功率。

正如傳統(tǒng)低頻拓撲結構所呈現的那樣,要從硅充電器獲得更多能量意味著更大的尺寸、更重的重量和更高的成本,設計的功率密度和熱密度都出現了瓶頸。

10年內智能手機屏幕尺寸和電池容量增加3倍以上

Oliver表示,智能手機屏幕、電池和5G功能的增加以及數據處理和傳輸速率和容量的增強,使人們開始關注充電速度及旅行適配器的尺寸、重量和成本。同時,引入單一、靈活的充電平臺(硬件和軟件),即帶電源傳輸(USB-PD)的通用串行總線“Type-C”連接器(USB-C)或可編程電源(PPS),意味著消費者不再依賴于OEM提供的電源產品。

他認為,提升功率密度的關鍵是提高開關頻率,盡量減少變壓器、EMI濾波器、大容量和輸出電容器等無源元件。早在1996年,像有源箝位反激(ACF)之類的高速拓撲自就已被學術界提出,但由于硅的不良導通電阻和開關性能及復雜性,又缺乏優(yōu)化控制IC而落地受挫。

2018年初,GaN功率IC的推出結束了這一局面,不僅使ACF具備了商業(yè)可行性,而且使智能手機充電器的高頻準諧振反激式充電,以及CrCM(臨界導通模式)升壓PFC(功率因數校正)拓撲結構、用于游戲筆記本電腦、一體式PC、電視和5G發(fā)射單元電源等更高功率系統(tǒng)的高速LLC(諧振控制器)和先進CrCM圖騰柱PFC具備了商業(yè)可行性。

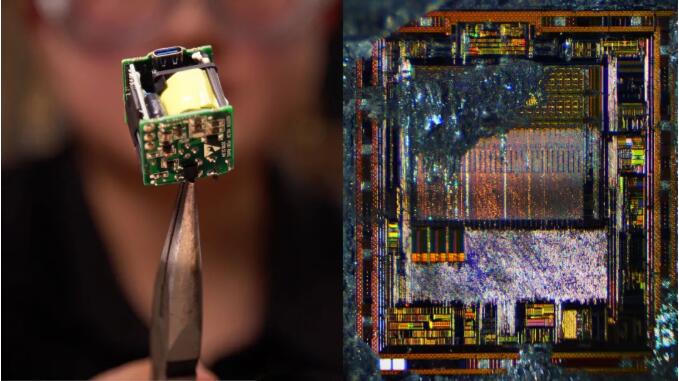

GaN功率IC在一個貼片封裝中集成了GaN功率FET和GaN驅動加控制和保護。這些GaNFast? 電源IC是易于使用、高速、高性能的數字輸入、輸出電源構件。由于柵極驅動回路基本上沒有阻抗,集成后關斷時幾乎沒有損耗。此外,還可以根據特定應用要求控制和定制開啟性能。

效果如何呢?GaN功率IC的運行速度比傳統(tǒng)硅設計快20倍,功率高3倍,并已被戴爾、聯(lián)想和小米等OEM用于智能手機和筆記本電腦的快速充電。從OPPO 50W Mini SuperVOOC Cookie快速充電器可以看出,高速GaN拓撲結構消除了無源元件,讓充電器尺寸為之減小。采用TI UCC28782控制器和一對半橋配置GaNFast功率IC實現了速度提高10倍的高效率有源箝位反激。

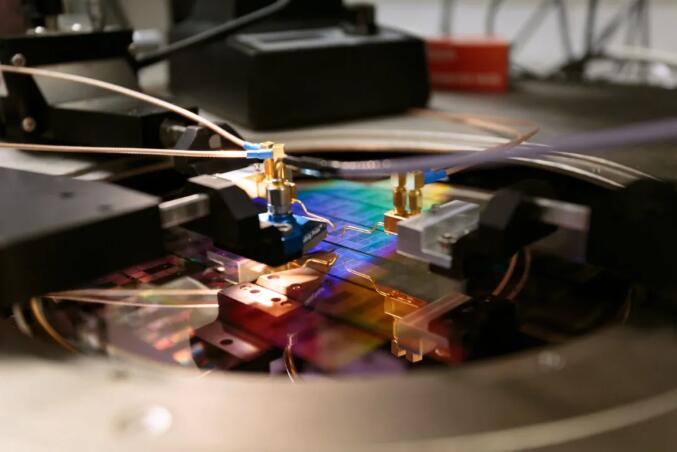

苛刻市場需求下的測試

圖源 | 網絡

“精心設計的電壓和溫度應力測試表明,GaN功率器件具有汽車和工業(yè)市場所要求的高可靠性,”Transphorm質量和可靠性副總裁Ron Barr這樣認為。

寬帶隙(WBG)氮化鎵的功率MOSFET的優(yōu)點使其在汽車電源子系統(tǒng)和數據中心電源等要求苛刻的場合發(fā)揮著越來越重要的作用。這些應用具有挑戰(zhàn)性的工作條件,且由于汽車保修成本或與數據中心可靠性相關的高成本,無法容忍出現故障。在選擇功率器件時,設計工程師必須確信其可靠、堅固和耐用。

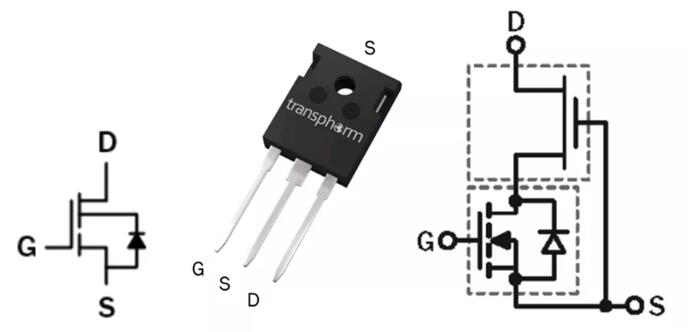

以Transphorm常關型雙芯片設計的耗盡型GaN HEMT(高電子遷移率晶體管)TP65H035WSQA為例進行測試和分析,將GaN HEMT與一個常關型低電壓硅FET串聯(lián)在一起,組成共源共柵器件結構。

共源共柵符號及共源共源器件組合結構

該器件采用TO-247封裝,在175℃下符合AEC-Q101標準。在評估產品可靠性時,設計工程師需要四個可靠性信息/數據“域”來確定器件是否適合應用,包括:產品認證;高加速壽命試驗;早期壽命失效試驗;現場可靠性。

產品認證

產品認證主要遵循兩個業(yè)界常用標準。JEDEC JESD 47適用于商用器件,更嚴格的AEC-Q101標準適用于車規(guī)器件。每個標準都有一系列產品必須通過的測試,如溫度循環(huán)、高溫反向偏壓、高溫柵極偏壓等,這樣的產品才能被視為JEDEC或Q101合格。

高加速壽命試驗

高加速壽命試驗(HALT)是一種定義明確的方法,即在有時超出其數據表極限的條件下對器件施加應力,直到器件失效,與此同時收集有關失效時間(TTF)的數據,以便應用適當的模型來預測耐用壽命(也稱固有壽命)。

在反向偏壓下,對處于關閉狀態(tài)的電壓介于1050V和1150V的批量650V額定電壓器件進行測試,直到大多數器件出現故障。然后計算在每一組條件下的平均失效時間。

圖源 | The Verge

以類似的方式,器件要在三種不同溫度下進行失效測試。三種不同電壓和三種不同溫度都是在加速測試條件下得到的。現在,每個測試的失效時間都在一組使用條件下進行了歸一化,條件通常源于應用的任務概要。在實例中,選擇了一組[敏感詞]條件來計算100%占空比條件下650V 175℃器件的壽命。

所有測試數據可以組合在一個模型中,稱為“使用圖”,該圖顯示了在使用條件下根據失效時間繪制的失效概率。

通常的做法是在失效概率為100PPM時定義器件壽命,這個實例中是連續(xù)運行100年,為106小時。

早期失效試驗

早期失效測試用來計算應用中的保修風險,并測試器件損壞前發(fā)生失效的概率。早期壽命失效(早期失效率)通常是由于制造過程中沒有發(fā)現或篩選出的缺陷而發(fā)生的,通常稱為“內在缺陷”。在GaN器件案例中,這些內在缺陷會導致電場畸變和缺陷位置的加速失效。

為了進行有意義的測試,應該嘗試測試比之前描述的HALT測試大得多的器件樣本,以增加發(fā)現內在缺陷的概率。使用的方法在JEDEC標準JESD 74A中有完整描述,可在JEDEC網站上獲得。

早期壽命失效通常以FIT(十億小時失效率)或PPM/年計算。數據表明,FIT率非常低,這可能預示著非常好的現場可靠性。

現場可靠性

Transphorm的現場可靠性計算遵循行業(yè)慣例,并考慮了交付的器件數量、現場使用多長時間以及客戶報告有多少器件失效。當然,并不是所有產品都能立即交付或使用,為了保守起見,將器件小時總數減半。Transphorm在現場的器件工作時間遠遠超過70億小時,迄今為止共有兩次退回,其現場可靠性不到1FIT。

“測試表明,上述GaN功率器件超過了汽車和工業(yè)OEM具有挑戰(zhàn)性的可靠性要求。這些GaN器件的可靠性至少與現有的硅和其他寬帶隙技術相當,而且往往更好,”Barr自信地總結道。

GaN柵極驅動的新要求

圖源 | Pinterest

“低功耗GaN是下一個革命性步驟,將為電力電子應用開辟一個新紀元。不過,使用新型功率晶體管技術需要注意一些問題,”英飛凌科技高級首席工程師Eric Persson指出。

功率開關在提高適配器性能、密度和成本方面的作用不可小視。傳統(tǒng)上,作為開關的功率晶體管是硅基的,趨勢清楚地表明,寬帶隙晶體管,特別是GaN正在成為高性能、小尺寸適配器的標準。

回顧功率晶體管技術的發(fā)展,直到今天,硅SJ(超結)晶體管一直是充電器/適配器中使用的主要晶體管技術。它可以提供低導通電阻、優(yōu)異的電流處理能力、簡單的柵極驅動,以及在小封裝中經過時間驗證的可靠性,所有這些都是低成本的。

然而,考慮到適配器所需的寬電壓范圍,以及由于漏感和雷擊電涌瞬變引起的過電壓瞬變,即使是650V晶體管往往也不夠用,需要700-800V的器件。而這正是GaN比硅具有顯著優(yōu)勢的一個方面。因為,當外加電壓超過額定電壓時,硅晶體管會進入雪崩擊穿狀態(tài)。一些設計使用“齊納”效應作為緩沖來抑制過電壓瞬變。但是,即使能量在晶體管的安全工作區(qū)(SOA)內,這種方法也會增加功率損耗,并可能導致產生額外的不良EMI(電磁干擾)。此外,浪涌產生的大量能量可能超過雪崩能量而損壞晶體管。

相反,GaN晶體管的額定電壓遠低于其實際破壞性擊穿電壓。晶體管的額定電壓基于規(guī)定應用條件,以滿足器件壽命所需的可靠性水平。例如CoolGaN? 600V e型HEMT,其破壞性擊穿電壓通常在1000V以上,在各種條件下,其脈沖電壓額定值為750V。在完美的ACF匹配拓撲中,泄漏能量由諧振電路管理,GaN的高脈沖電壓額定值可以調節(jié)雷擊浪涌電壓。

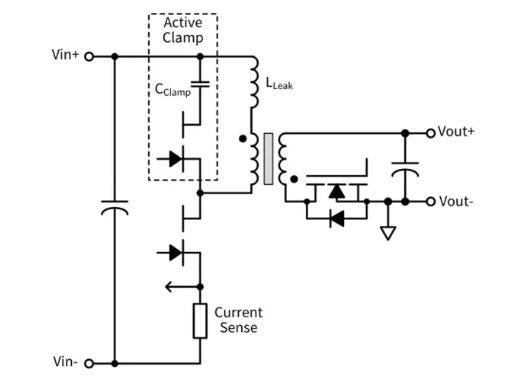

應用GaN晶體管的關鍵在于其柵極驅動的要求不同于硅晶體管。一個重要區(qū)別是GaN的閾值和全導通柵源電壓(VGS)明顯低于硅晶體管。雖然這減少了柵極電荷,但也可能在保持晶體管關閉方面出現挑戰(zhàn)。在ACF電路中,兩個晶體管被配置為半橋,主開關在底部,有源箝位作為高壓側開關。控制器和低邊晶體管驅動器由偏置電源供電。但是高壓側柵極驅動器需要一個浮動電源。在大型電信或數據中心電源中,可以用一個單獨的DC-DC轉換器為高壓側提供浮動偏置電源。但在適配器/充電器中,這種方法的尺寸和成本都令人望而卻步。

有源箝位反激拓撲簡化電路

為高壓側供電的一種常見方法是所謂的自舉(bootstrap)電源,即當低壓側接通時,高壓側偏置的儲能電容器通過二極管從低壓側偏置電源向上充電。當高壓側打開時,它會從儲能電容器中吸取偏置,且必須定期補充(每次低壓側打開時)。當電路連續(xù)工作時,這是為高壓側供電的一種非常有效和低成本的方法。但挑戰(zhàn)在于如何在不連續(xù)模式下操作。

那么,如何避免自舉電容器沒有充電時高側虛假開啟呢?一般的柵極驅動器IC有時包括一個箝位電路設計,但用于硅晶體管的傳統(tǒng)方法依賴于更高的閾值電壓(如3-4V),因此,如果電路在1-2V范圍內開始箝位,不幸的是,它們需要數百ns才能開始箝位。而GaN晶體管已經可以在這些柵極電壓下傳導大量電流。

為了優(yōu)化與GaN晶體管結合的快速箝位驅動器性能,必須最小化兩者之間的干擾阻抗。英飛凌采取集成高邊和低邊GaN晶體管(190m?)的方法,與新的半橋驅動器一起集成在一個iQFN 8×8mm封裝中,制作出半橋集成功率級(IPS)。

與競爭產品相比,這種集成和分區(qū)方法有以下優(yōu)勢:

不需要外部數字隔離器,傳播延遲很短(47ns)

高低側驅動器之間延遲的不匹配時間僅為幾個ns,因此可以安全且容易地將死區(qū)時間調整到最小,以獲得[敏感詞]效率

柵極驅動RC(電阻-電容)網絡在外部,允許調節(jié)開關速度以平衡損耗和EMI,通過隔離柵的電容非常小,降低了共模EMI電流

高側和低側驅動器完全隔離

寫在最后

發(fā)揮優(yōu)勢的時刻已經到來

以氮化鎵、碳化硅為代表的第三代半導體具備耐高溫、耐高壓、高頻率、大功率、抗輻射等優(yōu)異特性,工藝、成本等方面的限制正在慢慢消融,接下來就要看應用端如何通過器件測試、驅動開發(fā)、外圍元件配套發(fā)揮其優(yōu)勢了。

免責聲明:本文轉載自“與非網eefocus”,本文僅代表作者個人觀點,不代表薩科微及行業(yè)觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯(lián)系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1