服務熱線

0755-83044319

發布時間:2022-09-05作者來源:薩科微瀏覽:2056

前言:在芯片行業,人們經常用到IP這個詞,例如IP開發、IP交易、IP復用、IP廠商、IP提供商等。行外人對此詞可能覺得不明覺厲,不知所云。他們也許以為是說IP卡,也或者以為是互聯網技術中所說的IP地址,其實都不是。本文就專門科普一下,說說芯片行業中IP到底是個什么東西。

“IC、IP、IQ卡,通通告訴我密碼!”是電影《天下無賊》中范偉的一句經典臺詞。現實中沒有IQ卡,只有IC卡和IP卡。IC卡是指集成電路卡,也叫做芯片卡,例如銀行卡,電信卡、交通卡和社保卡等都是用芯片卡實現的。IP卡是一種運用了TCP/IP協議的網絡電話卡,IP卡早已被淘汰不用了。但是,TCP/IP協議作為互聯網通信的底層技術一直被使用,所以IP、IP地址等詞匯還經常可以聽到。這是[敏感詞]種IP,它是互聯網領域的技術詞匯,專指IP協議或者IP地址。

圖1.電影《天下無賊》中列車上打劫一場戲的場景

第二種IP是一個法律詞匯,它是知識產權(Intellectual Property)的英文簡稱。現代社會中,許多國家都十分重視知識產權保護。芯片行業是一個高度智力密集、資金密集的行業,因此該行業中知識產權的保護則顯得更加重要。芯片行業中的知識產權可稱為硅知識產權(Silicon Intellectual Property),簡稱SIP。SIP的保護形式主要包括專利權保護(Patent Protection)和集成電路布圖保護(IC Layout Protection)。

本文要介紹第三種IP,它既是一個技術詞匯,也是一種東西,是一種商品。它凝聚了芯片設計者的智慧,具有商品和知識產權的屬性,可以被推廣、銷售和應用。因此,芯片行業有IP開發、IP交易、IP復用等科技和商業活動,也有一些企業被冠以IP廠商、IP提供商的稱謂。

一、芯片行業的IP是指什么?

芯片行業中所說的IP,一般也稱為IP核。IP核是指芯片中具有獨立功能的電路模塊的成熟設計。該電路模塊設計可以應用在包含該電路模塊的其他芯片設計項目中,從而減少設計工作量,縮短設計周期,提高芯片設計的成功率。該電路模塊的成熟設計凝聚著設計者的智慧,體現了設計者的知識產權,因此,芯片行業就用IP核(Intellectual Property Core)來表示這種電路模塊的成熟設計。IP核也可以理解為芯片設計的中間構件。

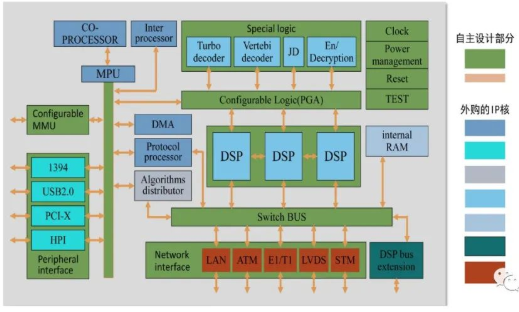

一般說來,一個復雜的芯片是由芯片設計者自主設計的電路部分和多個外購的IP核連接構成的。如圖2所示,要設計這樣結構的一款芯片,設計公司可以外購芯片中所有的IP核(不同顏色模塊),僅設計芯片中自己有創意的、自主設計的部分(用綠色表示),并把各部分連接起來。

圖2.自主設計部分和多個IP核集成在一起,形成復雜芯片的設計

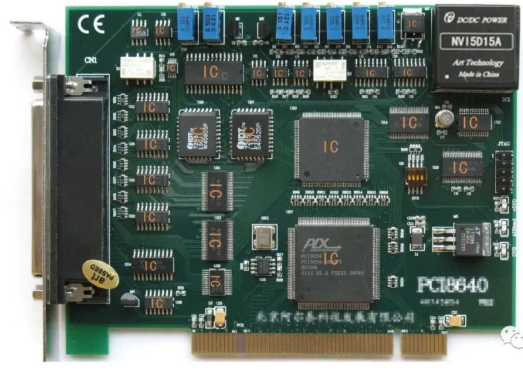

圖2的芯片設計過程就像圖3的系統電路板開發過程一樣,是用已有的、成熟的IP核(或者芯片)進行布局、擺放和信號連接的過程,這種過程可以稱為對IP核(或者芯片)的復用。不同的是,系統電路板上除了芯片和連接線之外,系統開發者很少自主開發自己的芯片。而在芯片設計過程中,芯片上除了采用外購的IP核之外,一般說來,芯片設計者還要設計一部分自己的電路,并完成各部分之間的信號連線,最后還要對整個芯片的功能、性能進行制造前的反復檢查和驗證。

圖3.由IP核搭建復雜芯片,與用芯片搭建完整的系統電路板類似

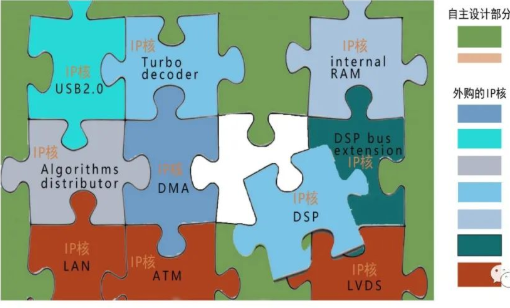

如果以上介紹還顯得太過專業,還可以用拼圖畫來對芯片設計打比方,可以把圖2所示的芯片抽象地理解成圖4所示的拼圖畫。芯片中外購的不同功能的IP核用不同色的圖塊表示,自主設計的電路部分用綠色圖塊表示,復雜芯片的設計過程就像要拼好這幅圖畫一樣。所相同的是,用現有的圖塊(IP核)拼接美麗圖畫(復雜芯片)。所不同的是,拼圖畫只要考慮圖塊的形狀,而芯片設計要考量IP核的許多參數和指標,并要把各個IP核和自主設計部分正確連接,保證整個芯片的功能和性能正確無誤。

圖4.IP核使復雜芯片的設計變得較容易,IP復用類似于“拼圖”

IP核被其他芯片設計公司采用,行業內稱為IP復用。專門設計相對獨立電路功能模塊,目的是推廣給其他芯片設計公司進行復用,這種設計工作稱為IP開發。專門從事IP開發的公司稱為IP廠商,或者IP提供商。IP廠商把IP銷售給芯片設計公司是一種IP交易行為。

二、IP的由來和作用

IP的由來要從早期的芯片設計過程講起。早期芯片的集成規模有限,設計復雜度不高,芯片上所有的電路都是由芯片設計者自主完成。設計水平不高、能力有限的芯片公司只能設計規模小的簡單的芯片。設計水平高、能力強的芯片公司才可以設計規模大、功能復雜的芯片。這個時期,不論芯片規模大還是小,芯片從“頭”到“腳”都是由芯片公司自己設計的。早期的高端芯片基本上都是由為數不多的大型國際芯片公司把持。

隨著現代信息社會對芯片要求提升,芯片的規模呈指數性增加,復雜性急劇增大。中小型芯片公司要獨立完成一款復雜芯片設計幾乎變得不太可能。特別是20世紀80年代末,芯片行業出現了晶圓代工(Foundry)商業模式,大批的中小微芯片設計公司(Fabless)應運而生。這個時期,芯片設計行業急需解決小芯片公司無法設計大芯片的難題。

解決這一難題的啟發思路很多。例如:搭積木和拼圖畫玩具;由標準件設計大型機器;由軟件子程序(或者中間件)調用設計大型軟件;用芯片搭建大型電子系統等。思路都是重復使用預先設計好的成熟的構件來搭建更復雜的系統,省掉對構件內部問題的考慮,化繁為簡;重復使用構件,減少重復勞動,節省時間;重復使用構件,提高整個復雜系統搭建的成功率。

芯片設計行業中的IP核開發和IP復用,就是在這些思路啟發下形成的。IP核就類似于上述的構件。IP核是預先設計好的具有獨立功能的電路模塊設計。有了IP核這種構件,大的復雜的芯片設計就變得較容易、周期短、易成功。

IP的作用主要有四個方面,一是使芯片設計化繁為簡,縮短芯片設計周期,提高復雜芯片設計的成功率。二是IP開發和IP復用技術使小公司設計大芯片成為可能;三是使系統整機企業可以設計自己的芯片,提升自主創新能力和整機系統的自主知識產權含量;四是使芯片設計行業擺脫傳統IDM模式,成為產業鏈上獨立的行業,促進了芯片設計業迅猛發展。

目前,許多中小微芯片設計公司雖然設計能力和水平有限,但出于搶占市場,縮短芯片設計周期的需要,會外購許多IP核來完成自己的芯片設計項目。業界的IP開發商、IP提供商數量不斷增加,也變得越來越專業。各種功能、各種類型的IP核不斷涌現。IP交易活動也日趨普遍,交易金額也越來越大。

三、IP的種類和舉例

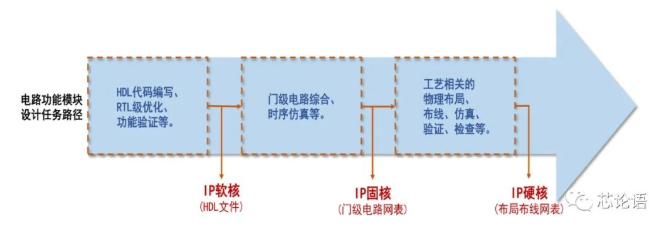

IP核有行為(Behavior)級、結構(Structure)級和物理(Physical)級三個層次的分類,對應著三個種類型的IP核,它們是由硬件描述語言設計的軟核(Soft IP Core)、完成結構描述的固核(Firm IP Core)和基于物理描述并經過工藝驗證的硬核(Hard IP Core)。

1.IP軟核:它是用硬件描述語言(HDL)設計的獨立功能的電路模塊。從芯片設計程度來看,它只經過了RTL級設計優化和功能驗證,通常是以HDL文本形式提交給用戶。所以它不包含任何物理實現信息,因此,IP軟核與制造工藝無關。

用戶購買了IP軟核后,可以綜合出正確的門電路級設計網表,并可以進行后續的結構設計,具有很大的靈活性。借助于EDA綜合工具,用戶可以很容易與其它IP軟核,以及自主設計的電路部分合成一體,并根據各種不同半導體工藝,設計成具有不同性能的芯片。

2.IP固核:它的設計程度介于IP軟核和IP硬核之間,它除了完成IP軟核所有的設計外,還完成了門級電路綜合和時序仿真等設計環節。一般地,它以門級電路網表的形式提供給用戶。

3.IP硬核:它提供了電路設計最后階段掩模級的電路模塊。它以最終完成的布局布線網表形式提供給用戶。IP硬核既具有結果的可預見性,也可以針對特定工藝或特定IP提供商進行功耗和尺寸的優化。

所以,三種類型的IP核是電路功能模塊設計在不同設計階段的產物,如圖5所示。

圖5.在電路功能模塊設計的不同階段,可得到不同類型的IP核

用戶經過精心評測和選擇,購買了IP廠商的IP核后,開始設計自己的芯片。前文講過,一個復雜芯片一般由購買的IP核和用戶自主設計的電路部分組成。芯片設計過程包括了行為級、結構級和物理級三個階段。行為級和結構級設計階段的工作一般稱為前端設計,物理級設計階段的工作一般稱為后端設計。圖6的示意圖說明,不同類型的IP核是在不同的設計階段中加入到整個芯片設計中去。

圖6.三種類型的IP核在芯片設計不同階段被合并到設計中,形成了一個整體

三種類型的IP核各有優缺點,用戶會根據自己的實際需要來選擇。以下是三種IP核的優缺點簡要總結。

IP軟核:它以綜合源代碼的形式交付給用戶,其優點是源代碼靈活,在功能一級可以重新配置,可以靈活選擇目標制造工藝。靈活性高、可移植性強,允許用戶自配置。其缺點是對電路功能模塊的預測性較差,在后續設計中存在發生錯誤的可能性,有一定的設計風險。并且IP軟核的知識產權保護難度較大。

IP固核:它的靈活性和成功率介于IP軟核和IP硬核之間,是一種折中的類型。和IP軟核相比,IP固核的設計靈活性稍差,但在可靠性上有較大提高。目前,IP固核是IP核的主流形式之一。

IP硬核:它的[敏感詞]優點是確保性能,如速度、功耗等達到預期效果。然而,IP硬核與制造工藝相關,難以轉移到新的工藝或者集成到新的結構中去,是不可以重新配置的。IP硬核不許修改的特點使其復用有一定的困難,因此只能用于某些特定應用,使用范圍較窄。但IP硬核的知識產權保護最為方便。

IP核的舉例,最典型有ARM公司的各種類型的CPU IP核。許多IP供應商提供的DSP IP核、USB IP核、PCI-X IP核、WiFi IP核、以太網IP核、嵌入式存儲器IP核等,五花八門,品種十分繁多。

如果按大類分,大體上可分為處理器和微控制器類IP、存儲器類IP、外設及接口類IP、模擬和混合電路類IP、通信類IP、圖像和媒體類IP等。

全球大的EDA供應商中,有些也是IP供應商。例如美國新思科技(Synopsys)可提供上千種各類IP。涵蓋邏輯電路(Logic Libraries)、嵌入式存儲器(Embedded Memories)、模擬電路(Analog Libraries)、有線和無線通信接口(Wired and Wireless Interface)、安全(Security)、嵌入式處理器(Embedded Processors) 和子系統(Subsystems)等方面的IP。

四、IP的開發和應用

從圖4、圖5可以看出,IP核開發與芯片設計過程比較相似,都需要緊跟芯片技術的發展趨勢,不斷積累芯片設計技術,了解芯片制造工藝發展步伐。所不同的是,芯片設計公司的商業模式是設計完整的芯片,并推向市場,實現芯片銷售利潤。而IP開發商不設計完整的芯片,他們只設計芯片局部的某些功能模塊,追求這些功能模塊(IP核)的設計是最優化的,并要實現IP核在多種復用場合的適應性、便利化。IP開發商謀求這些IP可以被眾多芯片設計公司購買采用,并實現IP的銷售利潤。

但是,IP開發的技術難度和要求很高,并不是任何芯片設計公司想為即可為的事情。這主要體現在,一是IP的完備性要求。IP核作為芯片設計的構件,可以與軟件設計的構件(中間件)作比較。軟件構件中可以隱藏小瑕疵,集成后的系統軟件還可以在投入實際應用時,通過打補丁升級的方式不斷完善。但IP核必須非常完善,一點瑕疵都不能有。因為,IP核的任何小瑕疵都有可能影響到整個復雜芯片設計的成敗,影響到花費了數百萬元甚至上億元整個芯片研發的投入產出。因此,復雜IP核的售價極為昂貴,從數十萬元到上百萬元不等。為了便于推廣,IP廠商一般采用收取前期IP許可費(IP License)+后期按芯片出貨量計算的版權費(Royalty)的商業模式,以降低用戶的研發投入。二是IP的多參數需求,包括工藝節點、電源、功耗、性能等。這些都要求IP開發者對芯片設計、制造工藝和行業應用等非常熟悉。三是用戶對IP提供商的信譽度要求,包括公司技術實力、影響力和穩定度等。用戶很難接受一家規模較小,發展不穩定的IP廠商提供的IP,哪怕這些IP很便宜,甚至免費。用戶寧愿購買[敏感詞]的、大的IP廠商提供的較貴的IP,因為這樣的IP才有質量保障和后續服務的保障。

2000年以來,在國發18號文件和八個[敏感詞]IC設計產業化基地的促進下,國內IC設計企業如雨后春筍般涌現,并得到快速發展。這些企業大部分是中小微IC設計企業,得益于IP開發和IP復用技術,這些中小IC設計企業都可以根據市場需要,及時開發出各種功能的系統級芯片(SOC)、人工智能(AI)芯片、物聯網(IoT)芯片等。這些推動了國內IC設計業的高速發展,帶動了我國新一代信息技術產業的發展。可以說,晶圓代工技術、IP開發和IP復用技術成就了我國目前芯片產業的快速發展基礎。

后記:芯片行業中所說的IP,也稱為IP核。IP核是指芯片中具有獨立功能的電路模塊的成熟設計。在電路模塊設計的三個不同階段,可以得到的不同類型的IP核,分別稱為IP軟核、IP固核和IP硬核。由軟化到固化,再到硬化,IP核的可配置性和靈活性變小,但完善性提高,復用風險性降低。芯片設計公司購買IP廠商的IP核,通過IP復用可以快速設計出功能復雜的芯片,可以節約設計時間,提高芯片設計成功率。IP開發和IP復用技術大大促進了芯片設計業的快速發展。

免責聲明:本文轉載自“芯論語”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1