DCDC+LDO到底解決了啥?

DCDC和LDO的優劣勢網上有很多資料不再贅述,DCDC+LDO這種結構[敏感詞]的優勢有兩個:

大部分DCDC在損毀如輸入電壓超限后輸入和輸出是短路的,直接接后級會造成整板損毀,損失較大,但LDO損毀后一般都是斷路狀態,這時候就能很好的保護后級降低損失。另外LOD對于低頻噪聲有很好的抑制作用。

LDO的PSRR

簡單地說,PSRR衡量電路抑制電源輸入端出現的外來信號(噪聲和紋波),使這些干擾信號不至于破壞電路輸出的性能。PSRR定義為:

其中,VEIN和VEOUTT分別是輸入端和輸出端出現的外來信號。對于ADC、DAC和放大器等電路,PSRR適用于為內部電路供電的輸入端。對于LDO,輸入電源引腳為內部電路供電的同時也為輸出電壓供電。PSRR具有與直流輸入電壓調整率相同的關系,但包括整個頻譜。

100kHz至1MHz范圍內的電源抑制非常重要,因為LDO經常跟高效的開關電源配合使用來為敏感的模擬電路供電。LDO的控制環路往往是確定電源抑制性能的主要因素。同時大容量、低ESR的電容也對電源抑制性能非常有用,特別是在頻率超過控制環路增益帶寬的情況下。

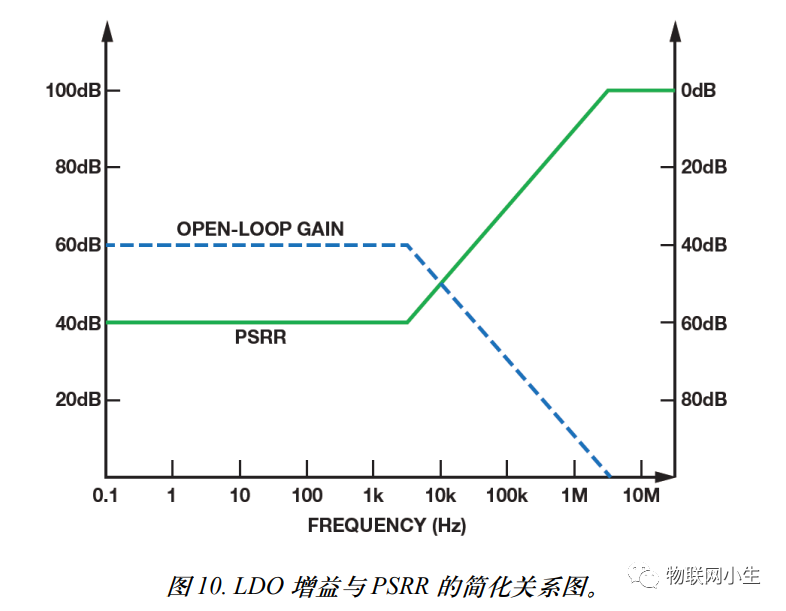

PSRR不是通過單一值來定義,因為它與頻率相關。LDO由基準電壓源、誤差放大器,以及MOSFET或雙極性晶體管等功率調整元件組成。誤差放大器提供直流增益以便調節輸出電壓。誤差放大器的交流增益特性在很大程度上決定了PSRR。典型LDO在10Hz時可具有高達80dB的PSRR,但在數十kHz時則可降至僅20dB。圖10顯示了誤差放大器的增益帶寬和PSRR之間的關系。這是一個簡化的示例,圖中忽略了輸出電容和調整元件的寄生效應。PSRR為開環增益的倒數,直到3kHz時增益開始下降為止。然后,PSRR以20dB/十倍頻程的速率降低,直到3MHz時達到0dB。

簡單的說,LDO對10k以下的噪聲有很好的抑制,同時電流越大,抑制效果越差。

DCDC的動態響應

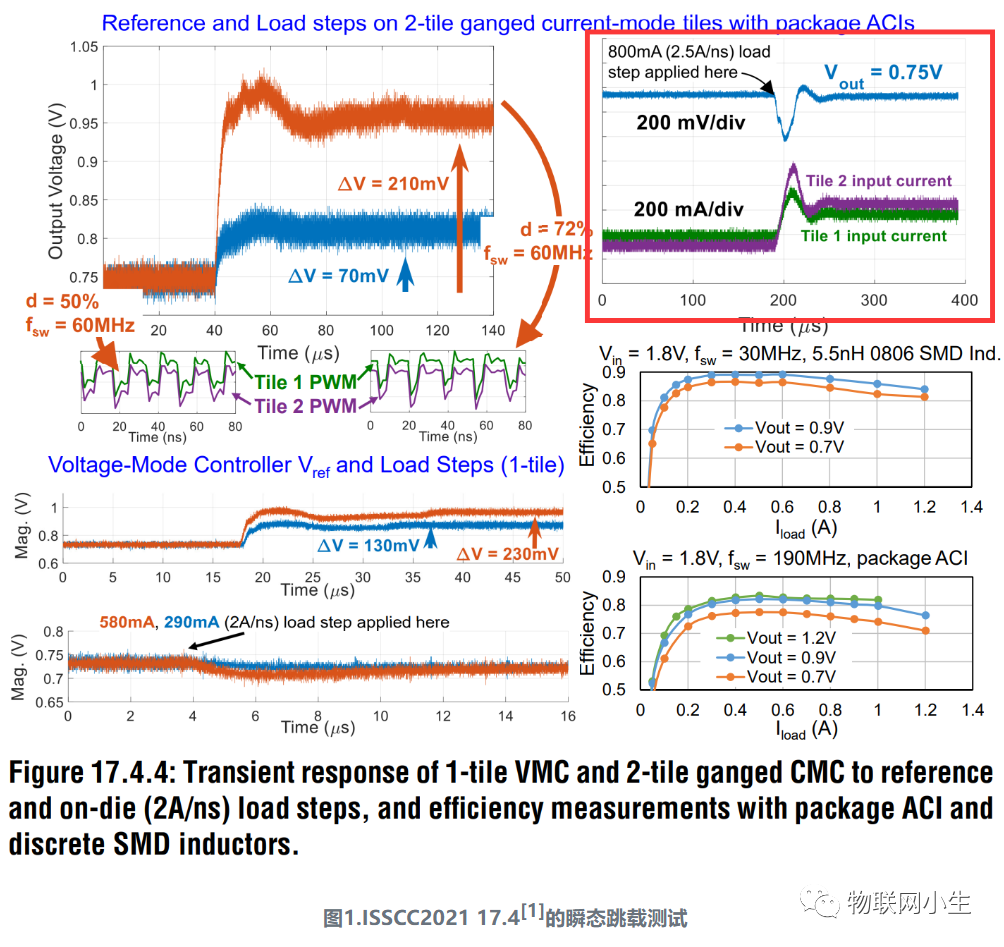

動態響應是指負載的動態響應或者說負載的瞬態響應Load Transient。

負載的動態響應是指負載電流突變時,輸出電壓是否能盡快穩定下來,動態響應考察的是輸出電壓VOUT和負載電流IL的關系。

負載突變的原因有很多,比如無線模組開機的瞬間或者發送數據的瞬間會有較大電流的變化,DCDC的動態響應考驗的是當負載有突變的時候輸出的電壓會不會跌落到啟動電壓以下造成系統重啟。如何優化電路的動態響應呢?

-

輸出端增加低ESR的大容量電容,當瞬間需要大電流的時候由電容提供一部分能量從而降低DCDC的壓力。

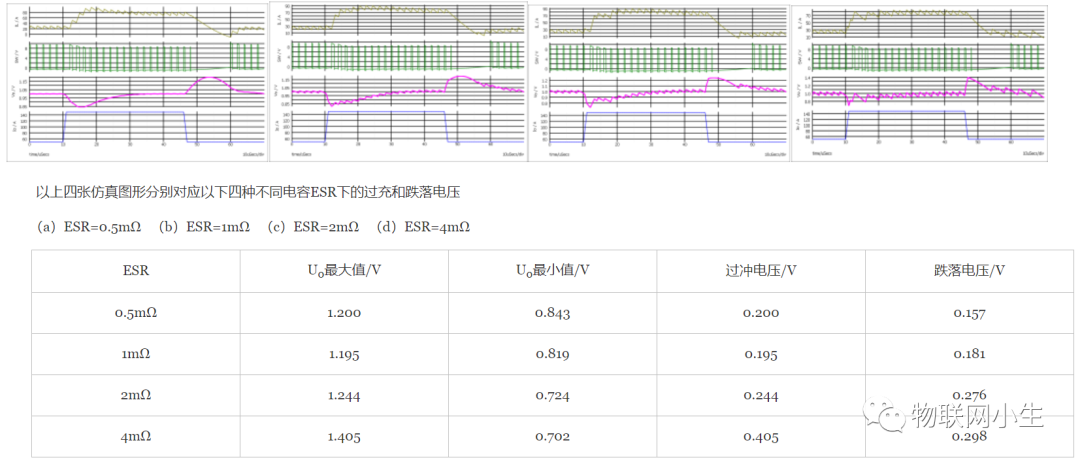

輸出濾波電容的等效電阻ESR對過充電壓和跌落電壓影響較大。因為,負載變化瞬間,電容快速充放電。ESR上產生的壓降不可避免。目前工藝,固態電容具有較低的ESR,可有效減小尖峰電壓。

-

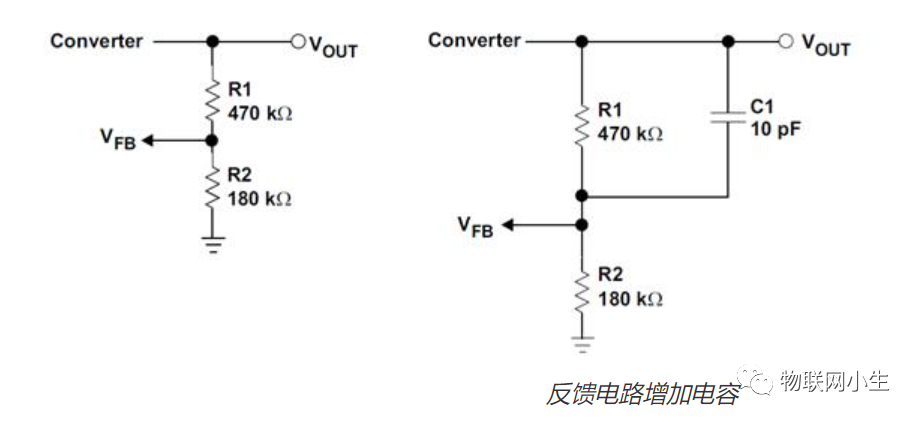

反饋電路增加前饋電容,從環路的角度講,并入一個電容,就是引入了一個零點和極點,其中零點低于極點。這樣會讓相位更平滑,當然帶寬也會相應變寬。比較兩種圖形不難發現,兩種反饋結構在低頻段具有一致的響應曲線;在中高頻區域,C1的通路阻抗降低使得輸出的電源擾動降到[敏感詞],有效的提供了更高的增益和相位。為了更多的抑制瞬態紋波,可以增大前饋電容的大小。對于運行中的DCDC電源轉換器來說,增益及相位的增加促使轉換器對瞬變負載產生更快的響應。

DCDC可以直接給MCU供電,當輸出電流較大的時候需要考慮動態響應問題。如果給模擬電路供電時可考慮增加高PSRR的LDO來抑制低頻噪聲。

免責聲明:本文采摘自“ 物聯網小生”公眾號,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。