服務熱線

0755-83044319

發布時間:2023-12-15作者來源:薩科微瀏覽:1759

這篇文章我們重點討論一下碳化硅MOSFET的驅動電路的設計考慮。包括碳化硅MOSFET隔離驅動要求、碳化硅MOSFET的驅動電流及驅動損耗計算、碳化硅MOSFET的驅動電流PCBlayout基本原則、碳化硅MOSFET的并聯設計考慮、碳化硅MOSFET的寄生開通效應及改善措施、碳化硅MOSFET在短路保護上的考慮和碳化硅MOSFET功率器件封裝上的考慮等內容。

一.碳化硅MOSFET隔離驅動要求

碳化硅MOSFET一般用于高壓,大功率電源應用,這種電源由于系統要求需要做原副邊的隔離,所以通過變壓器從一邊到另一邊傳遞能量,而控制器一般放在其中一邊,比如副邊,驅動原邊的碳化硅MOSFET的時候就需要通過隔離方式的驅動將副邊控制器發出的驅動信號,傳遞到原邊,去驅動它。

采用隔離方式,可以對原邊的高壓電路的地和副邊控制器的地,進行獨立的設計,避免高壓電路對低壓控制電路的損壞,同時,一些不希望的交流或者直流信號也不會從高壓側傳遞到低壓側,提高驅動電路的可靠性。這是碳化硅驅動電路的一個典型的要求。

比較傳統的隔離方式是光耦隔離,具有比較好的抑制瞬態和噪聲的能力,但是缺點是光耦的增益隨著時間會變化。另一種常見的隔離方式是磁隔離,但是在磁場環境中,應用會受到一定的限制。容性隔離也是較常見的隔離方式,對高壓及外部磁場的敏感度方面都有很大優勢,同時也支持快速開關運行,保持較小的延時。對于不同隔離方式的產品后續有機會再進行討論。

二.碳化硅MOSFET的驅動電流及驅動損耗計算

在高壓,大功率應用中,為了減小開關損耗,對驅動能力的要求更高,所以,對驅動器的驅動能力需要去提前評估。一般來說,對于一定開關頻率freq下,碳化硅MOSFET的門級電荷為Qg時,其對驅動電流的要求是freq×Qg,我們可以按照這個原則去對驅動芯片驅動能力做初步篩選。

進一步的,假設所需要驅動的碳化硅MOSFET并聯個數為N,每一個MOSFET的門級電荷為Qg,其門級驅動電壓為VGS,則總的驅動功率為freq×N×VGS×Qg,我們可以據此進行驅動損耗的估算。

在高壓及大功率應用下,一般碳化硅MOSFET的漏極的電壓DV/DT會很大,可以達到150V/nS,因此對于驅動器,希望它能夠驅動更高頻率,以[敏感詞]電流驅動器件的運行,所以一般建議保持最小的門級驅動輸出電阻,同時在高壓下,注意選擇CMTI(Common mode transient immunity)更大的產品。特殊情況下,需要進對驅動器輸出電阻行一定的優化,我們后續會介紹。

三.碳化硅MOSFET的驅動電流PCBlayout基本原則

在進行碳化硅MOSFET驅動電路時,也有一些類似于普通功率器件的layout原則需要注意,我們先來大致回顧一下。從寄生電感影響的角度來談的話,一般地,建議將碳化硅MOSFET器件和其驅動器線路盡量靠近,這樣就會減小門級驅動回路上的寄生電感。另外,盡量減小功率回路上的走線寄生電感,避免MOSFET開關在關斷時產生電壓尖峰和噪聲。

從寄生電容影響的角度來談的話,開關節點對地或者對固定電平地layout產生的寄生電容越大的話,會增加開關損耗,所以盡量避免在Layout時PCB層間耦合電容較大。另外,盡量減小開關節點和信號線路或者電壓總線的重疊,避免通過PCB層間容性耦合影響信號線路。

從磁場干擾的角度去分析,功率電流回路會產生高頻磁場干擾,磁元件也會產生高頻磁場干擾,一般盡量避免磁場對敏感信號線路的重疊或者空間上靠近,確保信號線路不受干擾。涉及到驅動線路的例子,如功率開關回路和驅動信號線之間就需要注意此問題。

四.碳化硅MOSFET的并聯設計考慮

大功率應用中,為了擴大功率,一般會涉及到MOSFET的并聯,這在SiMOSFET的時代就是一個很成熟的用法,不管是模塊電源中的低壓MOSFET,還是高壓大功率電源中的650V及以上的高壓MOSFET。在碳化硅MOSFET上,有一些設計方面需要特殊注意,接下來,我們會進行詳細討論。

并聯碳化硅MOSFET主要需要注意的問題是如何能夠很好的均流,因為只有很好的均流,才能讓損耗和熱量均衡,不至于超過其峰值電流限定或者熱保護限定。這里的均衡既包含穩態,也包含瞬態。其中涉及到的主要因素是器件個體Rdson及驅動開通門限VGS-th的差異,器件驅動電壓的不平衡,PCBlayout的不對稱等。

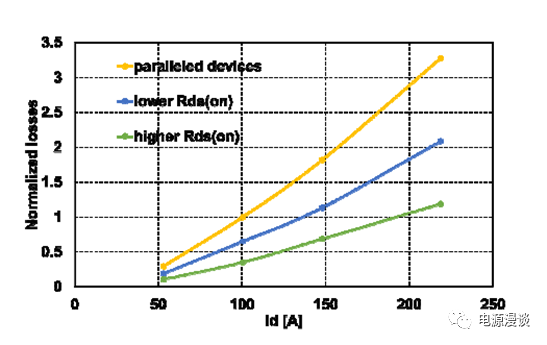

一個不均衡的因素就是并聯的碳化硅MOSFET器件的個體的導通電阻Rdson的不同導致的不均流,這會直接導致每一個器件上的電流不同,Rdson小的必然承擔更大的電流,從而導通損耗不相同。計算一下,如果Rdson有20%的變化,則較小導通阻抗的MOSFET會承擔1.5倍于較大導通阻抗的MOSFET的電流,所以二者的電流差異非常明顯。除了導通損耗的差異,由于穩態電流差異,則其在開關切換時的關斷電流也基于穩態電流有一定的差異,所以,造成一定的關斷損耗差異,如圖1,兩個1200V的50A的碳化硅MOSFET并聯測試關斷損耗歸一化數據,所示。這里兩個器件的Vds規格,VGS-th規格基本一致,但是Rdson相差20%。

圖1 高壓碳化硅關斷損耗不均衡測試-Rdson不同

類似于硅MOSFET的導通電阻正溫度系數的特性,碳化硅MOSFET也是如此,所以溫度越高,導通阻抗越大,承擔電流越小,這個特性對不均衡來說,是阻礙不均衡的,原本由于Rdson不均衡承擔較多電流的器件,會由于溫度升高,阻抗變大,從而承擔的電流減小,所以,這是一個好的方面。

導致電流不均衡的第二個因素是碳化硅MOSFET的導通門限電壓VGS-th,如果并聯的兩個器件的導通門限不同,對于同樣的驅動信號,則導通門限較小的器件先開通,而關斷時這個器件后關斷,這就造成在并聯的不同的器件上的損耗或者能量不均衡。

而在事實上,VGS-th這個參數隨溫度變化是負溫度系數,也就是說溫度越高,導通門限越低,所以,由于VGS-th不同導致的其中一個器件偏熱,隨著長時間運行,這個偏熱的器件,對應的VGS-th會更低,從而開關切換時間更長而變得更熱,這對于不均衡來說就是一個不利的方面。所以,如果在輕載時,或者以開關損耗為主導的應用中,若VGS-th差異較大,特別容易發生熱失控。

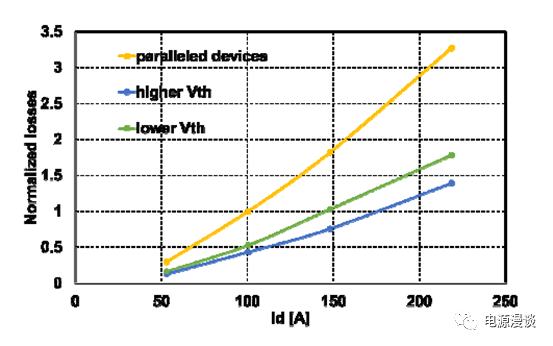

圖2 高壓碳化硅關斷損耗不均衡測試-VGS-th不同

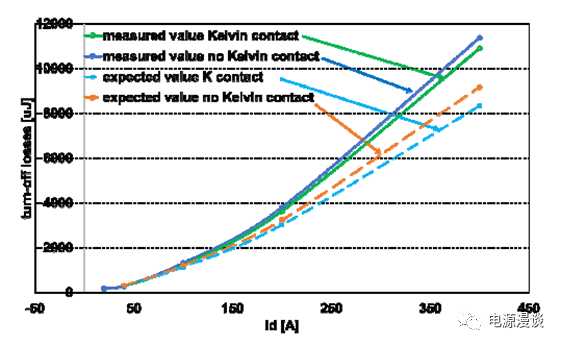

從上圖2中,可以看到兩個1200V,50A的高壓碳化硅并聯由于一定的VGS-th差異(700mV),而產生較大的關斷損耗。VGS-th差異造成的導通損耗差異影響較小,因為Rds-on本身的正溫度系數因素,這部分損耗差異可以得到一定補償。

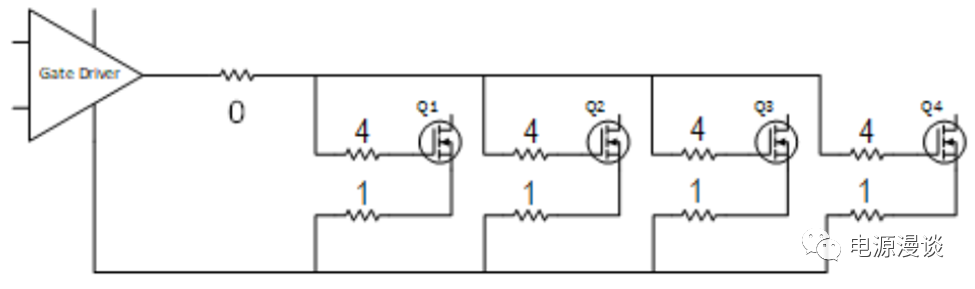

導致不平衡的第三個方面,主要是驅動電路方面的因素,一般的,為了減小開關損耗,希望以最快的速度開關器件,但是還要考慮門級震蕩問題,門級驅動電阻Rg和驅動線路的方式,對這些問題非常重要。

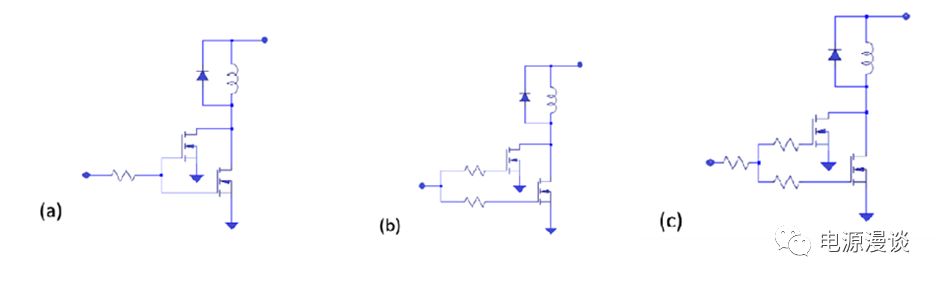

圖3 并聯開關器件的不同門級驅動方式

門級驅動線路,一般有以上幾種推薦方式,[敏感詞]種共用門級電阻的方式,不考慮其它不均流因素的情況下(如Rds-on,VGS-th等),其驅動信號同時到達,因此容易均流,但是共用驅動電阻會產生的RLC諧振容易產生門級震蕩。第二種方式,由于采取了分別的門級驅動電阻,不易產生門級震蕩,但是由于電阻差異,容易產生電流不均衡。所以比較推薦的方式,是采用第三種方式,既有共用的門級電阻,又有分別的驅動電阻,綜合[敏感詞]種和第二種方式,得到比較好的效果。

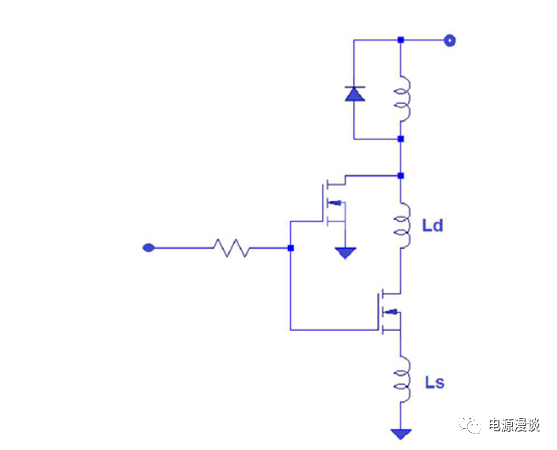

影響并聯均衡的第四個因素主要是layout造成的源極和漏極寄生電感的不平衡,如圖4所示,Ld和Ls分別是器件漏極和源極的寄生電感。

圖4 并聯器件的寄生電感

其中,Ls寄生電感,即源極寄生電感不平衡,是導致并聯器件不均衡電流的主要因素,而漏極電感對漏極電壓應力有比較大的影響,不在我們本次討論范圍內。所以,一般建議,盡可能地設計源極走線對稱,讓源極寄生電感對稱,或者減小其不匹配度,以避免電流不均衡。

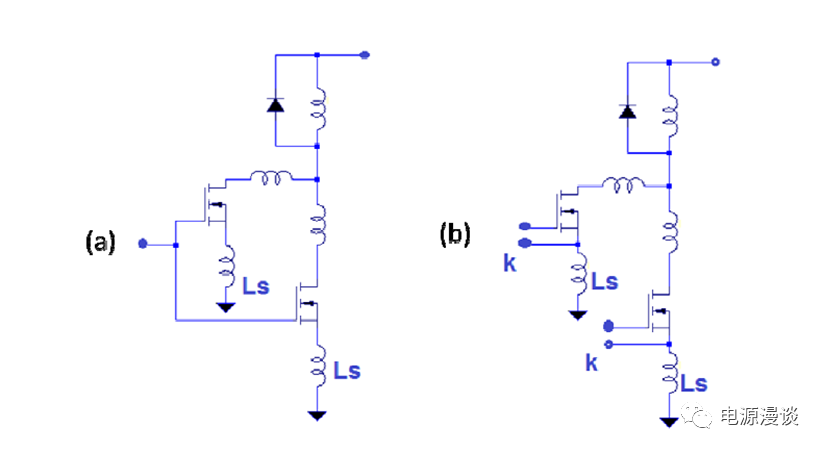

圖5 并聯器件a)無單獨源極連接b)有單獨源極連接

當器件進行開關切換時,較大的di/dt在源極寄生電感Ls上產生的電壓會反饋給門級驅動回路,所以當不采用如圖5,b所示的單獨源極連接時,會產生源極電壓的不平衡,會產生額外的開關損耗,也會導致一定的門級震蕩電壓。當采取了如圖5,b所示的單獨源極連接后,可以不用考慮Ls反饋電壓的影響,驅動信號不會加在源極寄生電感上。

圖6 開關損耗主導時的并聯時器件關斷損耗

在圖6所示的圖上,我們可知,當開關損耗占主導時,單個非并聯器件的關斷損耗之和是比二者并聯后總關斷損耗小的,從這個意義上講,開關損耗占主導時,并聯對減小損耗意義不大,但是可以有效的平均熱量分布。經過上述分析,我們可知,當開關損耗占主導時,由于沒有Rds-on的正溫度系數的平衡作用,若發生電流不平衡,則很容易發生熱失控。

圖7 減小并聯器件的門級震蕩電壓及均流電路

如果條件允許,如果沒有單獨的源極驅動連接時,可以在并聯器件的源極增加1ohm的串聯電阻,以實現動態均流,這可以減小大的漏極電流的di/dt,門級的串聯電阻RGoff,可以改善由于源極不平衡寄生電感造成的寄生震蕩。

五.碳化硅MOSFET的寄生開通效應及改善措施

在前一篇文章中,我們也簡要分析過半橋結構的碳化硅MOSFET的門級驅動波形一般要求,會考慮用負電壓去做可靠關斷,以避免較小的門級導通門限的影響,及一些不期望的門級耦合尖峰電壓出現導致的誤開通,但是一般碳化硅MOSFET的負電壓耐壓規格不像硅MOSFET那么大,所以使用需要嚴格遵守規格且考慮一定的裕量。在具體正/負電壓驅動的實施上,有多種方法可以實現,如多路隔離DC/DC電源,或者帶隔離DC/DC的隔離驅動器IC等。

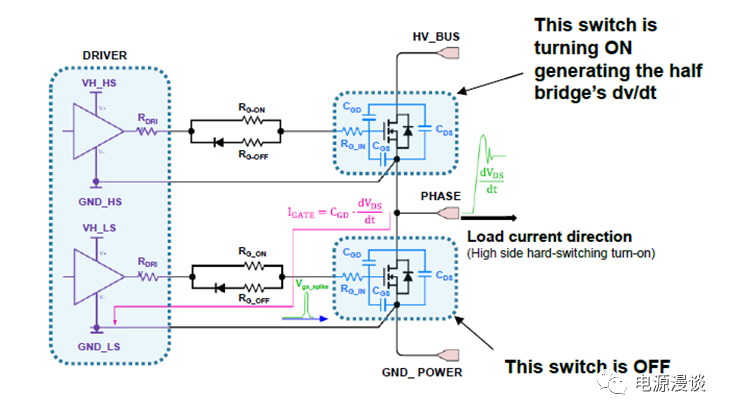

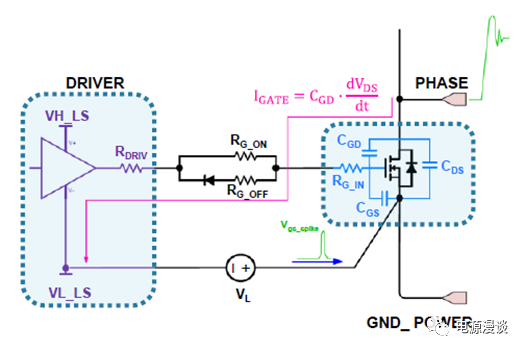

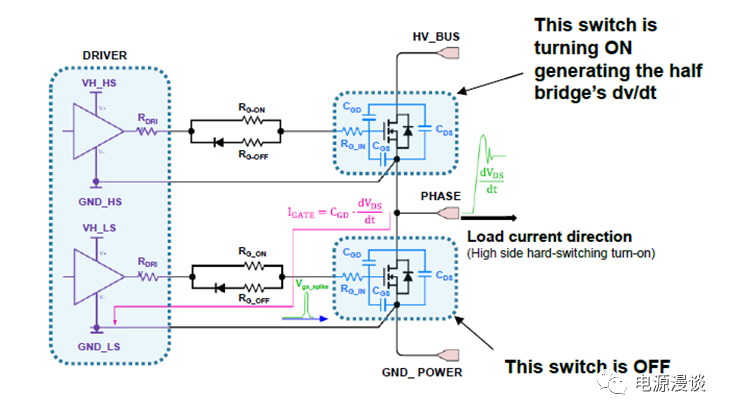

事實上,在用于大功率電路的典型的橋式電路拓撲中,半橋結構是基本的拓撲單元,如圖8所示,當上管開通時即下管關斷時,由于開關節點產生較大的dV/dT,所以這個電壓會通過碳化硅寄生電容CGD耦合到門級一個電壓脈沖,這個電壓脈沖一旦超過MOSFET的門級開通門限VGS-th值,就會產生誤開通,而我們知道VGS-th又是負溫度系數變化,溫度越高,門限越低,所以在高溫下會惡化這一點。一旦發生下管誤開通,那么勢必會產生上下管的短路直通,造成損耗增加。

圖8 快速的漏極dV/dT導致的米勒開通效應

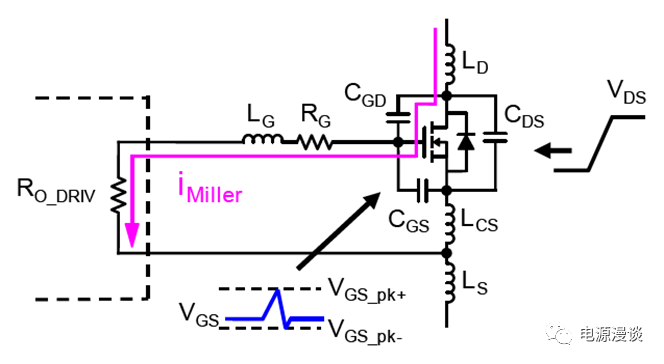

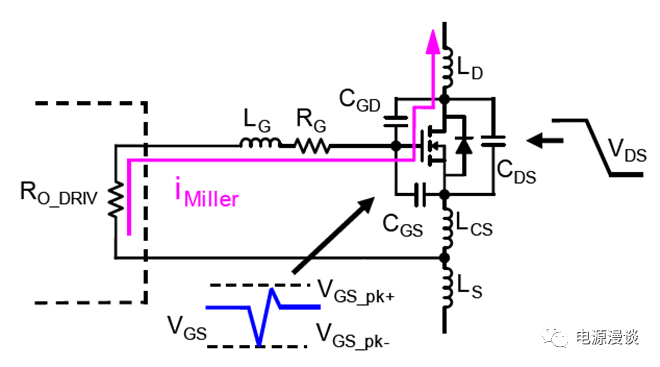

對于門級的尖峰電壓,分為兩種情況,上管開通下管關斷時,由于下管會有由低到高的快速dV/dT產生,所以如圖9所示,節點電壓通過CGD電容產生米勒充電電流,進而流過驅動器的輸出電阻在門級產生一個正的瞬態電壓,如圖9所示。

圖9 正的dV/dT電壓產生正的門級尖峰

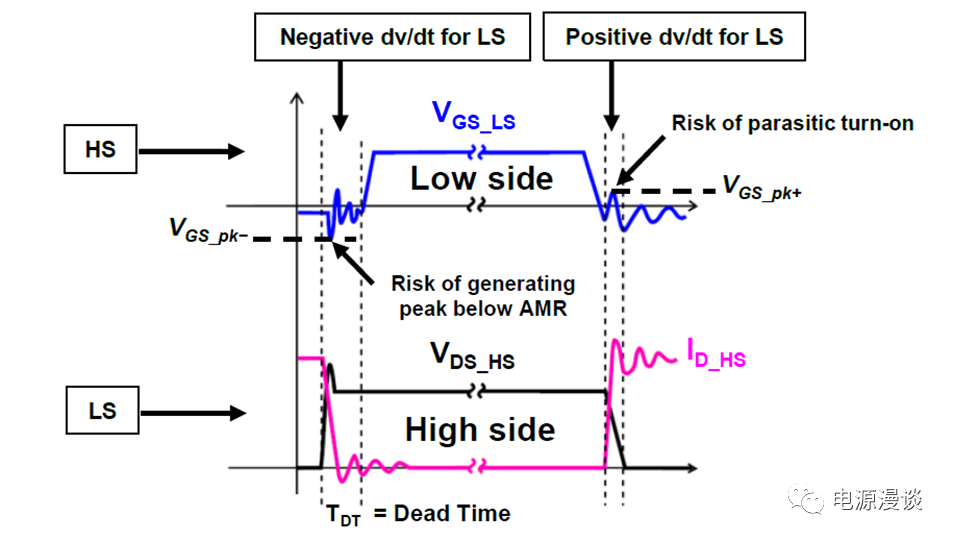

圖10 負的dV/dT產生反向門級尖峰

門級尖峰的另一種情況,是當上管關斷即下管開通時,開關節點產生由高到低的dV/dT,因此會產生反向的米勒充電電流,進而流過驅動器的輸出電阻,在門級產生負的電壓尖峰,這種情況需要注意負電壓尖峰是否超過負電壓耐壓規格。

圖11 器件寄生電容導致的正負門級尖峰電壓

從圖11上所知,下管驅動信號開通前的門級震蕩主要是負電壓,這部分電壓主要考慮對門級負電壓規格的限制,而下管驅動信號關斷后的門級震蕩主要是正電壓,這部分電壓主要會造成半橋短路問題,所以需要重點考慮。

寄生效應開通的原因我們解釋清楚了,那么,抑制這種效應的方式有哪些呢?通常來說,寄生效應開通是由于漏極的dV/dT較大而引起,所以限制dV/dT的變化率是一種抑制寄生開通效應的方式,但是這又和減小開關損耗的目標相矛盾。

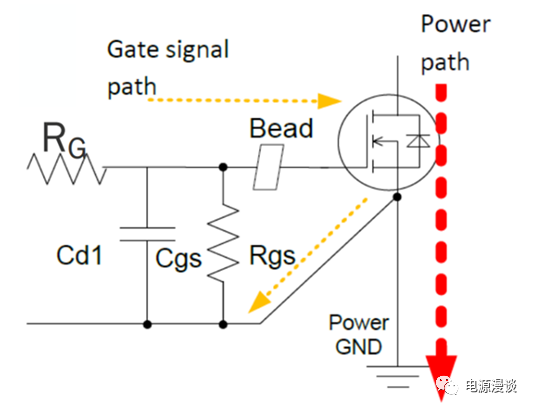

另外,在外部因素上,選擇低下拉電阻的驅動器及設置低關斷電阻RGoff,這樣可以讓米勒電流通過較低的阻抗通路,減小感應電壓的幅值。當然,像前一篇文章提到的,假如采用負電壓門級關斷電壓,也可以有效避免下管誤開通。

圖12 低阻抗關斷回路電阻

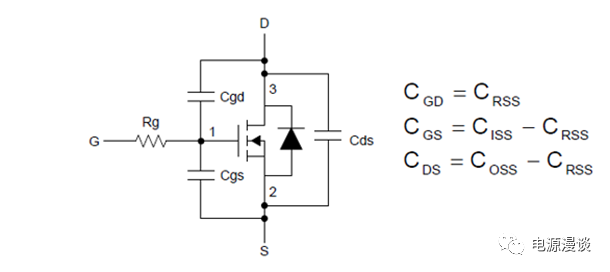

在器件本身上做文章,比如選擇CGS電容遠大于CGD電容的碳化硅MOSFET,這樣通過米勒電容的電流給門級電容充電就變得比較弱,如圖13所示,當然,也可以人為在門級并聯一個小電容,以減小米勒電容對門級電容的充電效應,如圖14所示,但是也會帶來更多的開關及驅動損耗。公開數據表明,高壓應用下,CGS和CGD的比例會比低壓應用下更大,所以更利于高壓應用。

圖13MOSFET寄生電容示意圖

圖14 增加門級電容避免寄生開通

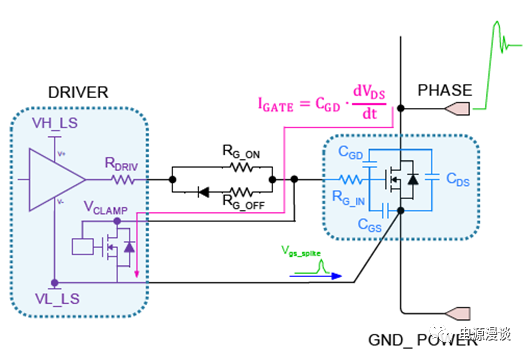

另一種有效的方法是,采用米勒鉗位電路,當檢測到門級電壓關斷尖峰后,開啟米勒鉗位電路,將門級電壓鉗位到GND,從而米勒電流不會通過驅動器輸出電阻將門級電壓抬高,這樣就可以使用0V電壓關斷碳化硅MOSFET,不需要使用負壓關斷,如圖15所示,為VCLAMP電路,一般這部分電路可以集成在驅動芯片中。

圖15 米勒鉗位電路

六.碳化硅MOSFET在短路保護上的考慮

碳化硅MOSFET的一個重要的參數是短路耐受時間(SCWT),由于這個參數涉及到器件安全,所以需要引起重視。由于碳化硅MOSFET的高電流密度,其芯片占用很小的面積,因此其短路耐受時間小于硅MOSFET,所以需要進行及時保護。

對于1個1200V耐壓的TO247封裝的碳化硅MOSFET,在700V的條件下,18V VGS驅動電壓,其短路耐受時間為8-10uS左右。在如此短時間內關斷碳化硅MOSFET的話,在漏極會引起非常大的dI/dT,從而導致大的漏極電壓尖峰,為了減小電壓尖峰,發生短路大電流時,一般建議慢速關斷VGS電壓。

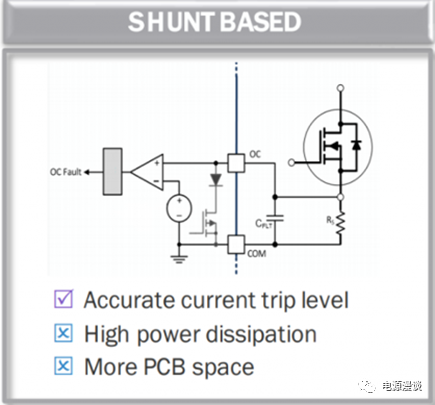

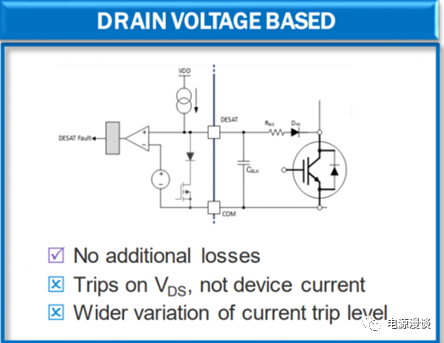

具體實施上,一般通過電流采樣電阻進行精確采樣,對發生短路的碳化硅MOSFET實施退飽和動作,但是這么做的缺點是造成額外損耗,并且采樣電路會增加PCB空間,所以僅僅用于小功率的應用,如圖16所示。在大功率應用中,一般使用Vds電壓作為采樣電壓去觸發過流保護,對器件進行退飽和,但是這種方式精度沒有那么高,因為通過Rdson采樣電流得到的Vds具有一定的變化范圍,如圖17所示。

圖16 采用Shunt電阻采樣的過流保護電路

圖17 采樣Vds電壓采樣的過流保護電路

采用Vds采樣設計過流保護電路是一個很講究的事情,因為需要同時兼顧觸發保護的及時性,也要避免誤觸發,對于前者,需要考慮Rdson的最差情況,以及溫度等因素。

典型的檢測退飽和的時間,一般是在電路開通之后250n-500nS左右檢測到信號,而保護關斷需要400n-1500nS左右的時間,事實上,需要在未發生飽和時(或者說還未達到電流峰值前),就需要能夠檢測到電流信號,而不能等到發生飽和時再檢測電流信號。

七.碳化硅MOSFET功率器件封裝上的考慮

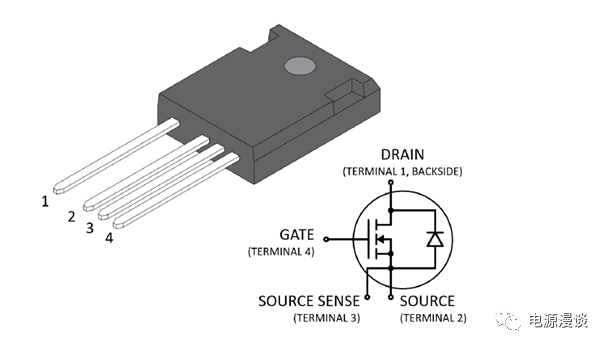

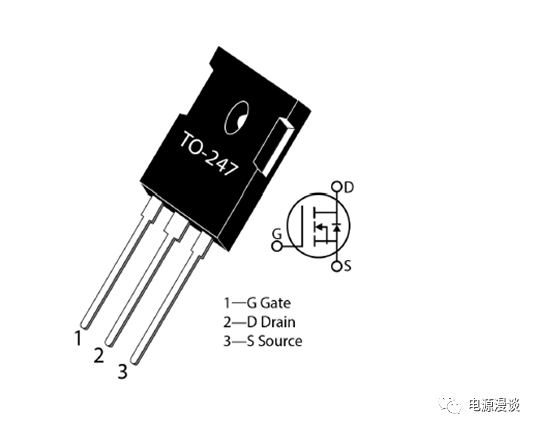

在高壓,大功率應用中,會用到如TO220或者TO247等插件封裝,因此在使用中,盡可能減小pin腳長度,以減小器件封裝帶來的寄生電感。

如前面碳化硅MOSFET并聯設計中討論過的一點,通過MOSFET源極單獨接線到驅動回路會顯著減小開關損耗。究其原因,是由于源極寄生電感會減緩開通過程或者關斷過程,增加開關損耗。所以,一般來說,TO247-4的封裝會比TO247的封裝開關損耗小30%。

具體分析這個過程,我們以半橋的上管為例,如圖18所示(將圖8搬到此處),當開關導通時,電流為從上到下,且逐步增加,則源極感應電壓為上正下負,這個電壓會讓門級驅動電壓減小,因此會減緩開通過程。同樣的,當上管關閉時,電流為從上到下,且逐步減小,所以源極感應電壓為下正上負,這會增加源極驅動電壓,因此會減緩關斷過程。這兩個狀態都會增加開關損耗,因此如果對開關損耗占主導或者較大,則考慮用TO247-4的封裝。

圖18 源極寄生電感對開關損耗的影響

從封裝圖上看,如圖19所示,TO247-4的封裝有一個單獨的源極的連接pin3,它和Gate pin相鄰,方便施加驅動信號,而漏極pin1和源極pin2的間距很大,這里需要承受Vds高壓。而TO247的pin腳安排相對簡單,G門級,D漏極,S源極順序排列。

圖19 TO247-4的碳化硅MOSFET封裝

圖20 TO-247的碳化硅MOSFET封裝

圖21碳化硅模塊的寄生電感的影響

在碳化硅MOSFET模塊的不同封裝中,合理設計得到較小的寄生電感,則對電壓過沖的限制非常有幫助,同時也會盡可能地提高產品運行開關頻率。

通過以上七部分內容的討論,從隔離驅動的基本要求,到驅動損耗計算,從單管寄生開通效應,到多管并聯實施,以及相應的layout原則,最后從封裝上提醒了若干注意事項。希望大家能對碳化硅MOSFET驅動電路方面的理解更加透徹,方便在實際方案中實施,以充分發揮碳化硅MOSFET的性能。

參考文獻

Designrules for paralleling of Silicon Carbide Power MOSFETs

Mitigationtechnique of the SiC MOSFET gate voltage glitches with Miller clamp

10Tings to Know About SiC

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1