服務熱線

0755-83044319

發布時間:2022-05-25作者來源:電源研發聯盟瀏覽:2240

選擇一個放大器的時候,電源范圍是首先要確定的指標,這由應用的需求來定,比如系統里其他器件的供電為單電源5V,那么如果放大器也可以單電源供電,那么對電源的設計就會簡單;如果系統的輸入信號比較大,比如±10V,那么此時放大器供電[敏感詞]為±15V。

芯片廠家在設計放大器時,電源范圍是多少,同樣也由應用需求決定。芯片廠家會研發相應的工藝來應對不同的電源需求。

放大器這一類產品發展了幾十年,市場需要什么樣電源范圍的產品,這些產品需要什么樣的工藝,基本已經定型。

探索無止盡,未來還會陸續涌現新的市場需求,促使廠商來改善工藝,來做出產品滿足市場。

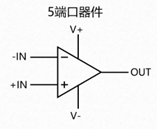

放大器電源分類

低壓:[敏感詞]供電電源<6V

中壓:[敏感詞]供電電源在10V~18V之間

高壓:[敏感詞]供電電源在24V~44V之間

超高壓:[敏感詞]供電電源>50V

要知道放大器的電源供電范圍,[敏感詞]的方法是查詢數據手冊——以器件ADA4077-2為例:

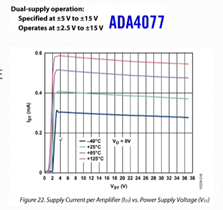

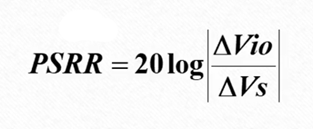

根據數據手冊可得Specifled 正負5V到正負15V,Opera-tes 正負2.5V 到正負15V,根據此參數進行評估測量就能征得ADA4077-2能否可以工作在+/-3.3V。

最小電源參考上圖,但僅供參考,無法保證。這張圖表中橫軸是供電電源,縱軸的是供電電流。對于不同的溫度,可以看到曲線的趨勢是基本一樣的,都是先上升,到一定階段之后就變平了。以- 40 度藍色的波形為例,該波形上升到大概可能 3.2 V 左右就開始變平。所以對于這個器件來講,在低溫工作時,最小供電電壓大約為3.2 V,當電源電壓更低時則無法正常工作。高溫的時候,最小的電源電壓可以更低。

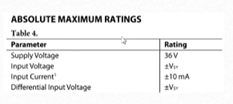

[敏感詞]參考下圖,absolute maximum ratings 描述了器件[敏感詞]的供電能超過36V。另外,實際設計時,需留有一定裕量,比如5%。

在某些器件的數據手冊描述中,可以能看到Single Supply的字樣描述,說明該器件是單電源放大器。

單電源放大器定義為輸入可以到負電源軌道的放大器,可簡化電源設計。比如V+接5V,V-接地的情況下,+IN可以接0V到地。

需要注意的是,不是所有的運放都是單電源放大器,但所有的運放都可以單電源供電工作,但要注意此時的輸入信號范圍和輸出信號范圍。

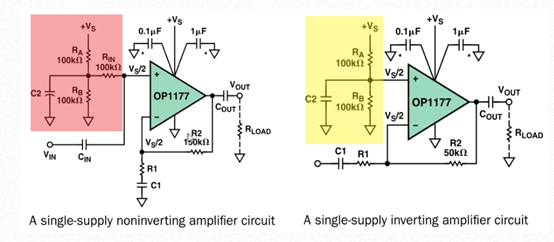

單電源放大器電路

單電源供電時的放大器電路往往需要特殊處理:為了使電路能調理正負信號,放大器輸入需要加入偏置電壓。以下圖為例,直流偏置電路在同相輸入端(紅色區域),由+Vs通過兩個100k電阻得到Vs/2的直流偏置電壓,電容C2決定了低通截止頻率,當C2為0.1uF時,截止頻率為32Hz(1/(6.28*50k*0.1u)=32Hz),如果使用更大的電容可以濾出更多的噪聲,使得直流偏置信號更干凈,但更大的電容意外上電后,輸出需要更長的時間來穩定到Vs/2。由于放大器電路也會對偏置進行放大,因此在電路的下半增益部分加入了電容C1。反相放大電路(圖右)也可同理進行分析。

單電源供電缺點

為實現更大的動態范圍,需要選擇較貴的單電源運放或是軌到軌運放。

直流偏置電路中的電阻會帶來額外的噪聲。

偏置電流流過直流偏置電阻會引入額外的直流電壓誤差。當然可以在負輸入端加電阻來做平衡使得偏置電流的影響抵消,但有的運放是無法抵消的,且增加的電阻會帶來噪聲。

為了濾除噪聲加的大電容,使得直流偏置電路的時間常數很大,導致上電后輸出會緩慢爬升到Vs/2。

0V和-5V供電可以嗎?

以LTC2066為例,這是一個供電范圍為1.7V~5.25V的放大器,一般使用正負 2.5 伏供電,或者+5V和0V供電,那是否可以使用零伏和負五伏來提供給正電源和負電源管腳供電呢?

上圖為LTC2066的簡單框圖,一般放大器是沒有配置地管腳的,這與很多其他類型的芯片是不一樣的。即使是單電源供電中-V接地,而非真正地有接地管腳。放大器就是這么定義的。它只需要知道待調理的信號,或是調理完的信號,與+V和-V供電電源有一定的相對關系,就能正確無誤地完成它的功能。(注意+V--V需要是正信號,且在放大器允許的電源范圍內)通過LTspice進行仿真,使用0V和-5V供電的情況下,可以發現該器件能夠正常工作,參數指標沒有受到影響。

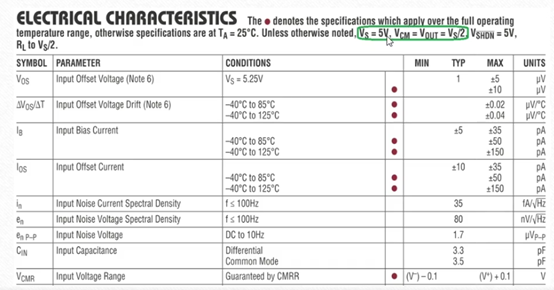

在測試放大器參數指標時,一般是雙電源供電進行測試。根據LTC2066芯片資料,其中Vs=5v,vcm=Vout=Vs/2,實際在測試時,采用的是±2.5V供電,輸入共模信號為0V。放大器輸入信號和輸出信號處在其允許范圍的最中間時,表現是[敏感詞]的。

用0V和-5V供電給+V和-V時,如果輸入共模信號為-2.5V那么此時的參數指標可以參考上圖。此時輸出信號只能是負信號,輸出只能是灌電流。

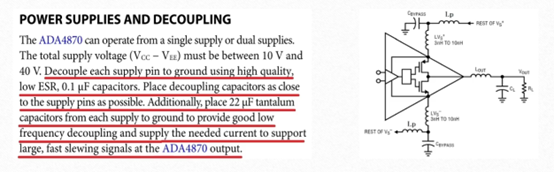

大多數的芯片資料都會提到有關去耦電容的建議,不加去耦電容有可能電路能正常工作,但非常不建議。

一般情況下,可以用0.1uF的去耦電容,放在放大器電源管腳附近,電容一端接電源管腳,另一端就近接地,低容值電容的高頻特性較好,可以移除高頻噪聲避免進入放大器。在電路位置不夠時,可以用幾個放大器共用一個大電容。

在需要低頻去耦或是放大器輸出快速變化的大信號時,需要大容值的電容(注意電容的額定電壓需要大于電源電壓)

儲能的角度說明電容去耦

只要電容足夠大,只需很小的電壓變化,電容就可以提供足夠大的電流,滿足負載瞬態電流需求,從而保證負載芯片電壓的變化在容許范圍內。這里,電容預先存儲了一部分電能,在負載需要的時候釋放出來,此時電容擔負的是局部電源的角色。

假設在低頻段,比如10kHz,低頻信號在電感上產生的感抗可以忽略,電容的ESL(寄生電感)可以近似等于0。當負載瞬間(10kHz)需要大電流的時候,電容可以通過ESR向負載供電,供電的實時性很高,ESR只是消耗了一部分電量,但不影響供電的實時性。由于頻率比較低,放電時間比較長(頻率的倒數),所以電容的容量大一些,可以長時間放電。

同樣大的電容,假設負載突變的頻率較高(幾十MHz),那么當負載瞬態變化的時候ESL上形成的感抗不容忽視,這個感抗會產生一個反向電動勢去阻止電容向負載供電負載實際獲得電流的瞬態性能比較差,電容電流無法供應瞬間的電流突變。盡管電容容量很大,但由于ESL較大,此時的大容量儲能發揮不了作用。頻率較高,電容給負載供電的時間縮短(頻率的倒數),不需要電容有大的儲能要降低電容的ESL,選擇小封裝的小電容,另外走線對于高頻,關鍵的因素是ESL,長度引入的電感也會折算到ESL參數里,所以小電容一定要靠近pin。

輸入為1V時,有無去耦電容的波形影響

去耦電容選多大

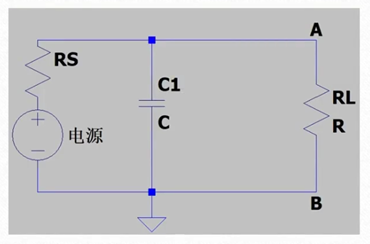

既然去耦電容可以幫助輸出波形更加平整,在電路中必不可少,那么如何選取容值呢?可以從阻抗的角度來理解電容去耦,其中C1為去耦電容:

從AB兩點向左看過去,穩壓電源以及去耦電容一起,可以看成一個復合的電源系統。理想情況下,不論AB兩點間負載需要的瞬態電流如何變化,電源都可以保證AB兩點間電壓保持穩定。這就要求電源系統的輸出阻抗Z要足夠低。通過去耦電容可以達到這一要求,可以說去耦電容降低了電源系統的阻抗。從電路原理的角度來說,可得到同樣結論。電容對于交流信號呈現低阻抗特性,因此加入電容,實際上也確實降低了電源系統的交流阻抗。

同理,也可以根據目標阻抗計算電容量,以該電路為例:要去耦的電源為40V,容許電壓波動0.05%,瞬態電流500mA

目標阻抗Zx=40V*0.0005/0.5=0.04

假設負載頻率是1MHz

4uF電容阻抗=0.040(C=1/(6.28*1M*0.04)=4uF)

負載頻率處于電容自諧振點以上時

電容阻抗由ESL決定

假設ESL為1nH去耦電容的[敏感詞]有效頻率

0.04/(6.28*1n)=5.3MHz

負載頻率降低時,需要的去耦電容容值更大

根據以上計算。可得電容最小要4uF,才能保證低阻抗,并且ESL要小,ESL直接影響去耦電容的[敏感詞]有效頻率。

需要注意的是,以上內容均為理論計算,實際應用中還需要驗證實測以獲得[敏感詞]選值。

如果要選DC-DC

電源芯片有很多指標,從影響放大器性能的角度看,DC-DC的開關頻率紋波及噪聲指標比LDO都要差很多(100kHz~2MHz開關頻率,200mVpp最差紋波)

一般來說,在對精度或噪聲有要求的場合,建議用LDO來為放大器供電。

如果傾向于DC-DC電源的其他諸多優點,那么可以由開關頻率紋波幅度,噪聲水平,再結合選定放大器的電源抑制比PSRR+和PSRR-,來簡單分析電源波動時對放大器輸出(輸入)的影響,是否在容忍范圍內。最后盡量進行一次實測,以判斷DC-DC電源是否會對放大器產生影響。

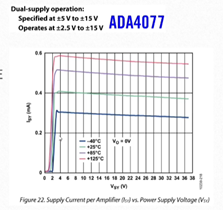

PSRR定義為電源波動時對放大器輸出(輸入)的影響,△Vio為輸出的變化,△Vs為電源的波動。理想情況下,△Vs不會對△Vio產生影響。

以上圖所示的PSRR圖表所示,可以看到開關頻率在100kHz的情況下,PSRR約為40dB,如果電源紋波為100mV,根據公式就可以計算出輸出紋波為1mV。

在某些應用中,既要求[敏感詞]性能,又得考慮電源效率(DC-DC電源更好),需要實測來驗證。

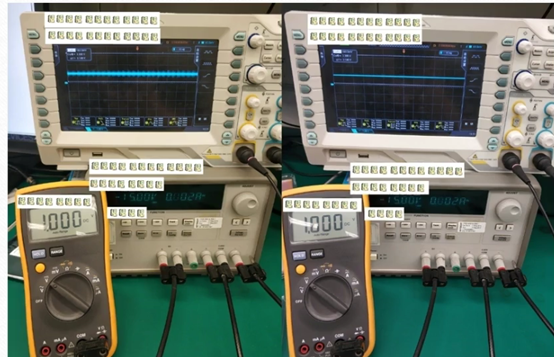

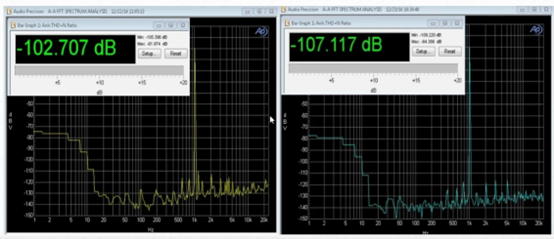

下面左圖是用很好的DC-DC電源為放大器供電,測得的THD+N,右圖是LDO供電的THD+N,THD+N相差4.4個dB。

可得出結論為DC-DC電源表現不錯,但比LDO還是差一點,需要按照實際的需求選擇供電的方式。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1