引言

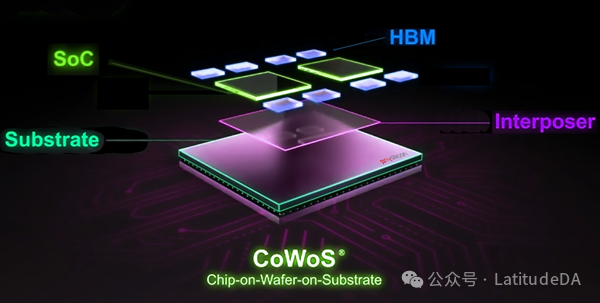

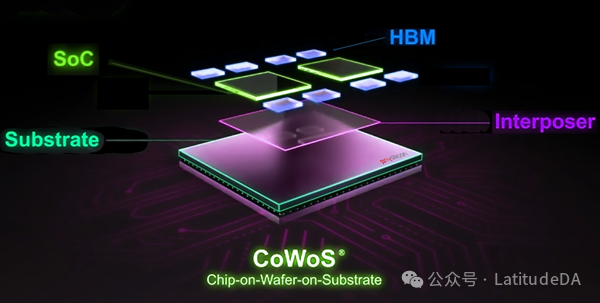

為了滿(mǎn)足高性能計(jì)算(HPC)和人工智能(AI)的計(jì)算需求,人們需要一種可擴(kuò)展的封裝。片上基板(CoWoS)是一種先進(jìn)的封裝技術(shù),具有封裝尺寸更大、I/O 連接更多的優(yōu)勢(shì)。它允許 2.5D 和 3D 組件堆疊,實(shí)現(xiàn)同質(zhì)和異質(zhì)集成。以前的系統(tǒng)面臨內(nèi)存限制,而當(dāng)代數(shù)據(jù)中心則采用高帶寬內(nèi)存(HBM)來(lái)提高內(nèi)存容量和帶寬。CoWoS 技術(shù)可在同一集成電路平臺(tái)上實(shí)現(xiàn)邏輯 SoC 和 HBM 的異質(zhì)集成。

圖片來(lái)源: 臺(tái)積電

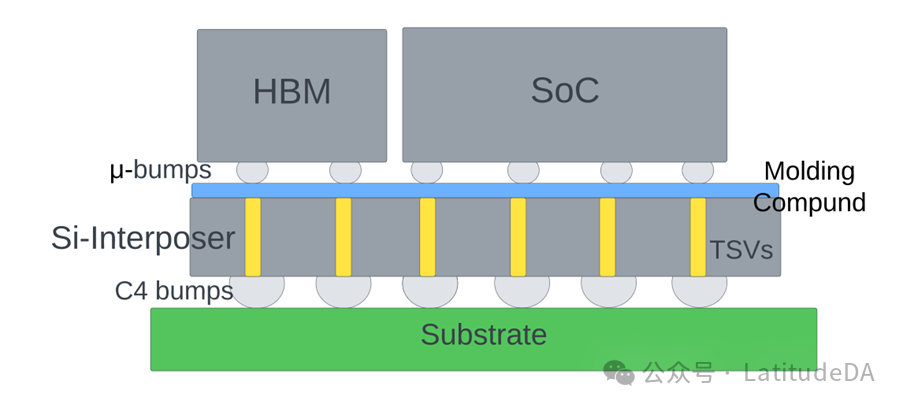

CoWoS 架構(gòu)包括 2.5D 水平堆疊和 3D 垂直堆疊配置,徹底改變了芯片封裝的傳統(tǒng)模式。這種創(chuàng)新方法允許逐層堆疊各種處理器和內(nèi)存模塊,創(chuàng)建相互連接的芯片,形成一個(gè)內(nèi)聚系統(tǒng)。通過(guò)利用硅通孔(TSV)和微凸塊,與傳統(tǒng)的二維封裝方法相比,CoWoS 可縮短互連長(zhǎng)度、降低功耗并增強(qiáng)信號(hào)完整性。

在實(shí)際應(yīng)用中,CoWoS 技術(shù)可將 GPU 和人工智能加速器等高級(jí)處理單元與高帶寬內(nèi)存(HBM)模塊無(wú)縫集成。這種集成對(duì)于人工智能應(yīng)用尤為重要,因?yàn)樵谌斯ぶ悄軕?yīng)用中,大規(guī)模計(jì)算能力和快速數(shù)據(jù)訪(fǎng)問(wèn)是最重要的。CoWoS 將處理元件和內(nèi)存元件就近配置,[敏感詞]限度地減少了延遲,提高了吞吐量,從而為內(nèi)存密集型任務(wù)帶來(lái)前所未有的性能提升。

CoWoS 技術(shù)具有多種優(yōu)勢(shì):

圖片來(lái)源: 臺(tái)積電

CoWoS 架構(gòu)包括 2.5D 水平堆疊和 3D 垂直堆疊配置,徹底改變了芯片封裝的傳統(tǒng)模式。這種創(chuàng)新方法允許逐層堆疊各種處理器和內(nèi)存模塊,創(chuàng)建相互連接的芯片,形成一個(gè)內(nèi)聚系統(tǒng)。通過(guò)利用硅通孔(TSV)和微凸塊,與傳統(tǒng)的二維封裝方法相比,CoWoS 可縮短互連長(zhǎng)度、降低功耗并增強(qiáng)信號(hào)完整性。

在實(shí)際應(yīng)用中,CoWoS 技術(shù)可將 GPU 和人工智能加速器等高級(jí)處理單元與高帶寬內(nèi)存(HBM)模塊無(wú)縫集成。這種集成對(duì)于人工智能應(yīng)用尤為重要,因?yàn)樵谌斯ぶ悄軕?yīng)用中,大規(guī)模計(jì)算能力和快速數(shù)據(jù)訪(fǎng)問(wèn)是最重要的。CoWoS 將處理元件和內(nèi)存元件就近配置,[敏感詞]限度地減少了延遲,提高了吞吐量,從而為內(nèi)存密集型任務(wù)帶來(lái)前所未有的性能提升。

CoWoS 技術(shù)具有多種優(yōu)勢(shì):

-

擴(kuò)展性和更高的集成度: 傳統(tǒng)上,按照摩爾定律擴(kuò)展晶體管有助于滿(mǎn)足對(duì)更高性能的需求。但事實(shí)證明,這對(duì)于高性能計(jì)算(HPC)、人工智能甚至圖形處理器(GPU)等現(xiàn)代應(yīng)用來(lái)說(shuō)是不夠的。CoWoS 允許在同一基板上堆疊芯片,從而減少同質(zhì)或異質(zhì)邏輯 SoC 之間以及 HBM 之間的互連延遲。

-

增強(qiáng)熱管理: 硅內(nèi)插件和有機(jī)內(nèi)插件的使用大大增強(qiáng)了堆疊集成電路的熱管理能力。這直接提高了整個(gè)系統(tǒng)的可靠性和壽命,同時(shí)[敏感詞]限度地降低了熱節(jié)流風(fēng)險(xiǎn)。

-

改善電源完整性: 堆疊集成電路內(nèi)的電源/接地網(wǎng)絡(luò)使用 RDL,同時(shí)使用深溝槽電容器 (DTC),使高速應(yīng)用和內(nèi)存密集型應(yīng)用的電源完整性不受影響。

-

縮小尺寸,降低成本:CoWoS 技術(shù)有助于將多個(gè)邏輯 SoC 和 HBM 安裝在相同的集成電路和基板上。這與傳統(tǒng)封裝技術(shù)形成鮮明對(duì)比,在傳統(tǒng)封裝技術(shù)中,多個(gè)邏輯 SoC 需要安裝在一塊印刷電路板(PCB)上,并在封裝中進(jìn)行必要的連接。這導(dǎo)致封裝尺寸增大,材料成本和制造費(fèi)用增加。CoWoS 封裝整體更小,成本效益更高。

CoWoS 技術(shù)的市場(chǎng)動(dòng)態(tài)

人工智能、云計(jì)算、大數(shù)據(jù)分析和移動(dòng)計(jì)算等技術(shù)的蓬勃發(fā)展導(dǎo)致對(duì)計(jì)算能力的需求日益增長(zhǎng)。

現(xiàn)代社會(huì)對(duì)計(jì)算能力的高需求促進(jìn)了人工智能芯片的發(fā)展,推動(dòng)了對(duì) CoWoS 等先進(jìn)封裝解決方案的需求。

TrendForce 的數(shù)據(jù)顯示,人工智能服務(wù)器出貨量大幅增長(zhǎng),2023 年達(dá)到近 120 萬(wàn)臺(tái),預(yù)計(jì) 2022 年至 2026 年的復(fù)合年增長(zhǎng)率為 22%。

對(duì)人工智能芯片的需求,尤其是對(duì)采用更高規(guī)格 HBM 的 GPU 的需求,導(dǎo)致臺(tái)積電 CoWoS 封裝的產(chǎn)能緊張,英偉達(dá)是其主要客戶(hù)。

由于供應(yīng)短缺,臺(tái)積電的 CoWoS 封裝能力一直是人工智能芯片產(chǎn)出的瓶頸,尤其是在中間件領(lǐng)域。

臺(tái)積電計(jì)劃將 CoWoS 產(chǎn)能提高一倍,并投資先進(jìn)的封裝廠,以期在 2024 年底前緩解供需失衡問(wèn)題。

包括聯(lián)電、日月光科技控股公司和力成科技在內(nèi)的其他臺(tái)灣公司正在進(jìn)入 CoWoS 高級(jí)封裝市場(chǎng),擴(kuò)大產(chǎn)能并提供替代解決方案。

目前使用的 CoWoS 技術(shù)分為三類(lèi):

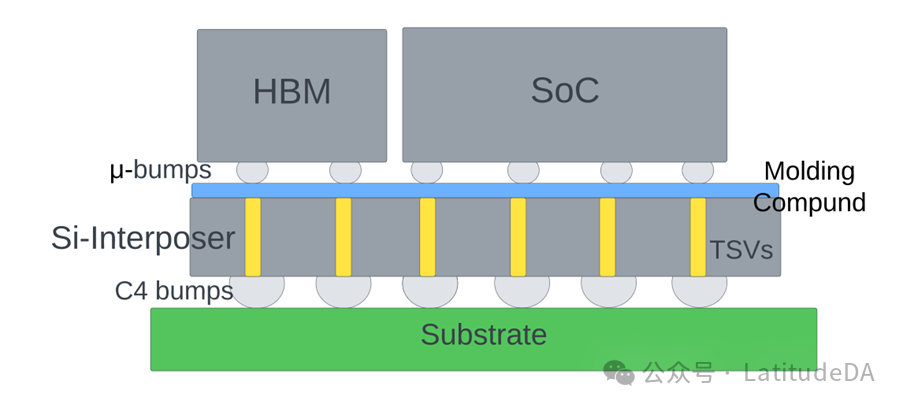

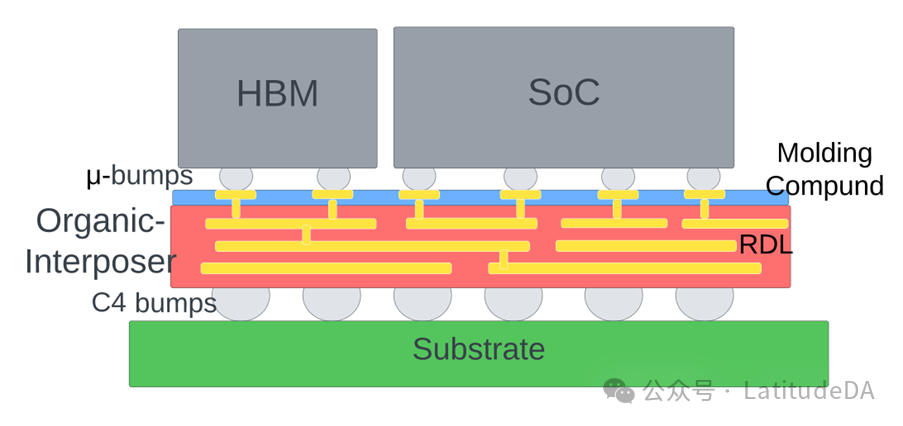

CoWoS-S:該技術(shù)使用單片硅內(nèi)插件和硅通孔(TSV),以促進(jìn)芯片和基板之間高速電信號(hào)的直接傳輸。不過(guò),單片硅內(nèi)插層存在良率問(wèn)題。

圖 1:CoWoS-S 封裝

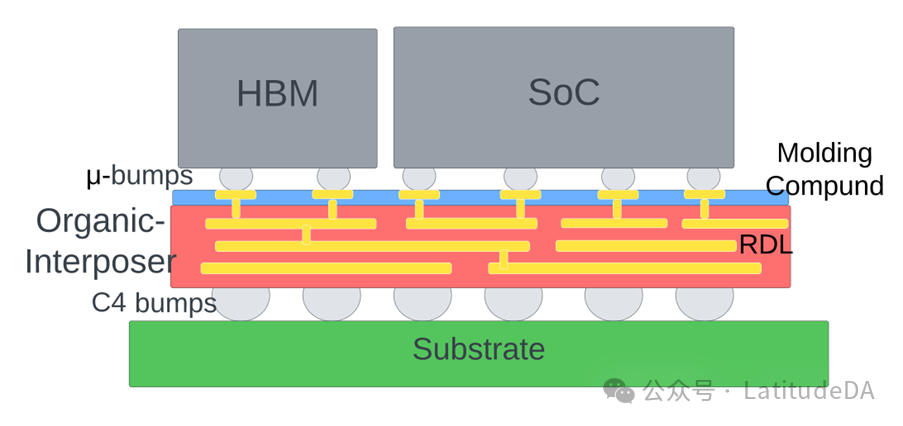

CoWoS-R:這項(xiàng)技術(shù)用有機(jī)插層取代了 CoWoS-S 的硅插層。有機(jī)插層具有細(xì)間距 RDL,可在 HBM 和芯片甚至芯片和基板之間提供高速連接。與 CoWoS-S 相比,CoWoS-R 具有更高的可靠性和成品率,因?yàn)橛袡C(jī)中間膜本身具有柔性,可作為應(yīng)力緩沖器,減輕因基板和中間膜之間的熱膨脹系數(shù)不匹配而產(chǎn)生的可靠性問(wèn)題。

圖 1:CoWoS-S 封裝

CoWoS-R:這項(xiàng)技術(shù)用有機(jī)插層取代了 CoWoS-S 的硅插層。有機(jī)插層具有細(xì)間距 RDL,可在 HBM 和芯片甚至芯片和基板之間提供高速連接。與 CoWoS-S 相比,CoWoS-R 具有更高的可靠性和成品率,因?yàn)橛袡C(jī)中間膜本身具有柔性,可作為應(yīng)力緩沖器,減輕因基板和中間膜之間的熱膨脹系數(shù)不匹配而產(chǎn)生的可靠性問(wèn)題。

圖 2:CoWoS-R 封裝

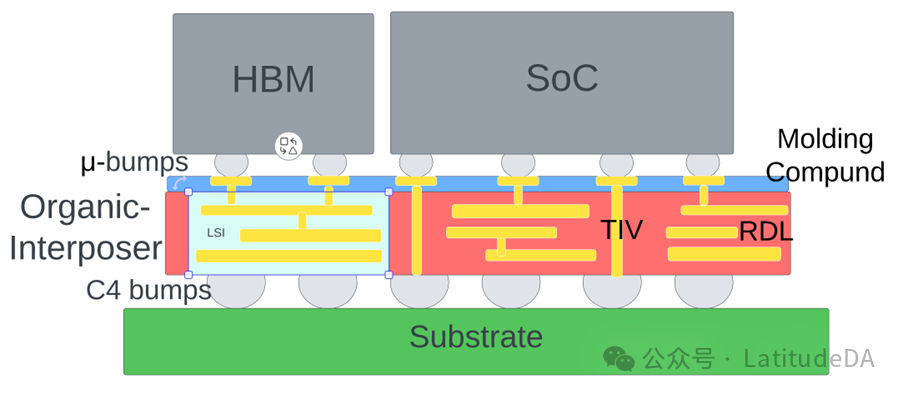

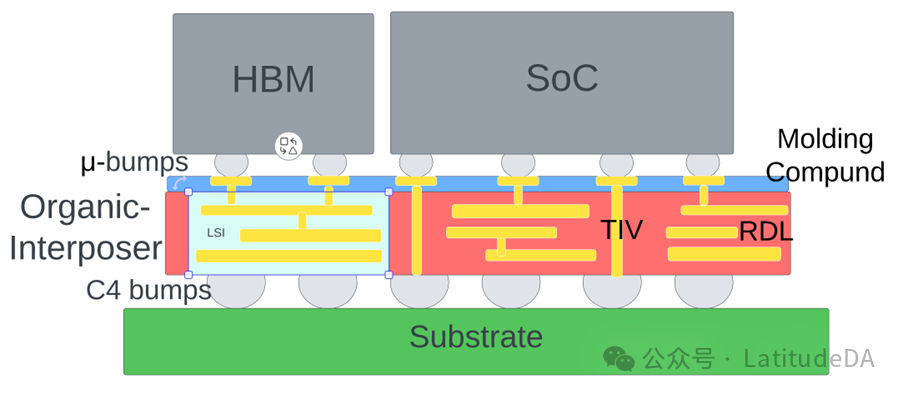

CoWoS-L 封裝:這種封裝使用本地硅互連(LSI)和 RDL 內(nèi)插件,共同構(gòu)成重組內(nèi)插件(RI)。除了 RDL 內(nèi)插件外,它還保留了 CoWoS-S 的誘人特點(diǎn),即硅通孔 (TSV)。這也緩解了 CoWoS-S 中由于使用大型硅內(nèi)插件而產(chǎn)生的良品率問(wèn)題。在某些實(shí)施方案中,它還可以使用絕緣體通孔 (TIV) 代替 TSV,以[敏感詞]限度地降低[敏感詞]損耗。

圖 2:CoWoS-R 封裝

CoWoS-L 封裝:這種封裝使用本地硅互連(LSI)和 RDL 內(nèi)插件,共同構(gòu)成重組內(nèi)插件(RI)。除了 RDL 內(nèi)插件外,它還保留了 CoWoS-S 的誘人特點(diǎn),即硅通孔 (TSV)。這也緩解了 CoWoS-S 中由于使用大型硅內(nèi)插件而產(chǎn)生的良品率問(wèn)題。在某些實(shí)施方案中,它還可以使用絕緣體通孔 (TIV) 代替 TSV,以[敏感詞]限度地降低[敏感詞]損耗。

圖 3:CoWoS-L 封裝

本節(jié)將討論 CoWoS-L 封裝的組成和制造步驟:

圖 3:CoWoS-L 封裝

本節(jié)將討論 CoWoS-L 封裝的組成和制造步驟:

1.CoWoS-L 是一種芯片末端組裝,因?yàn)槭紫纫圃熘虚g膜,然后在上面堆疊晶圓芯片。中間膜是 CoWoS 技術(shù)的關(guān)鍵原材料之一,因?yàn)槎鄠€(gè)晶圓芯片(如 SoC、HBM 等)都安裝在中間膜上,中間膜實(shí)現(xiàn)了芯片之間的有效連接和通信。中間膜制作完成后,下一步就是在晶圓裸片上制作直通絕緣通孔(TIV)。

2.然后在晶圓上安裝已知良好芯片(KGD)。晶粒和 TIV 之間的間隙用模塑化合物填充,然后使用 CMP 工藝獲得平面。

3.下一步是制作兩個(gè) RDL 層

除此之外,CoWoS-L 技術(shù)還使用了深溝電容器 (DTC),可提供高電容密度,從而提高系統(tǒng)的電氣性能。這些電容器可充當(dāng)電荷庫(kù),滿(mǎn)足運(yùn)行高速計(jì)算應(yīng)用時(shí)的瞬時(shí)電流需求。

CoWoS 是一種 2.5D/3D 集成技術(shù),與其前代產(chǎn)品相比,制造復(fù)雜度較高。制造復(fù)雜性直接導(dǎo)致采用這種封裝技術(shù)的芯片成本增加。這被認(rèn)為是近來(lái)高性能計(jì)算和人工智能芯片成本增加的一個(gè)重要原因。CoWoS 的測(cè)試成本也增加了總成本。

5D 和 3D 集成電路需要像其他集成電路一樣進(jìn)行測(cè)試,以確保它們不存在任何制造缺陷。然而,測(cè)試 2.5D 或 3D 集成電路的難度要大得多,因?yàn)樵趯⒚總€(gè)晶圓裸片安裝到插接器上之前,都需要對(duì)其進(jìn)行單獨(dú)測(cè)試,安裝后還需要再次測(cè)試。除此之外,還需要對(duì)硅通孔(TSV)進(jìn)行測(cè)試。最后,大型硅內(nèi)插件特別容易出現(xiàn)制造缺陷,并可能導(dǎo)致成品率下降。

CoWoS 封裝存在熱問(wèn)題,這是因?yàn)橹虚g膜與基底之間的熱膨脹系數(shù) (CTE) 不同。使用有機(jī)中間膜可在一定程度上限制熱問(wèn)題。使用底層填充材料可以緩沖硅芯片和基底之間的熱失配,從而大大延長(zhǎng)焊點(diǎn)的使用壽命。

同樣,在正面,再分布層(RDL)的完整性,尤其是兩個(gè)硅芯片下面的再分布層,很容易受到應(yīng)力的影響。使用 μ-bump 底部填充材料可在硅芯片和 RDL 之間起到應(yīng)力緩沖作用。

CoWoS 封裝面臨信號(hào)和電源完整性方面的電氣挑戰(zhàn)。

(1)信號(hào)完整性:

邏輯晶片-芯片-基板互連: 隨著數(shù)據(jù)速率的提高,TSV 的寄生電容和電感會(huì)導(dǎo)致互連信號(hào)傳輸性能下降。為解決這一問(wèn)題,我們努力優(yōu)化 TSV,以盡量減少電容和電感。

邏輯晶圓-晶圓到 HBM:SoC 和 HBM 之間互聯(lián)的眼性能瓶頸在于互聯(lián)的寄生電阻和電容。

CoWoS 封裝通常用于具有較高數(shù)據(jù)切換率和較低工作電壓的高性能應(yīng)用。因此,這些封裝容易受到電源完整性挑戰(zhàn)的影響。

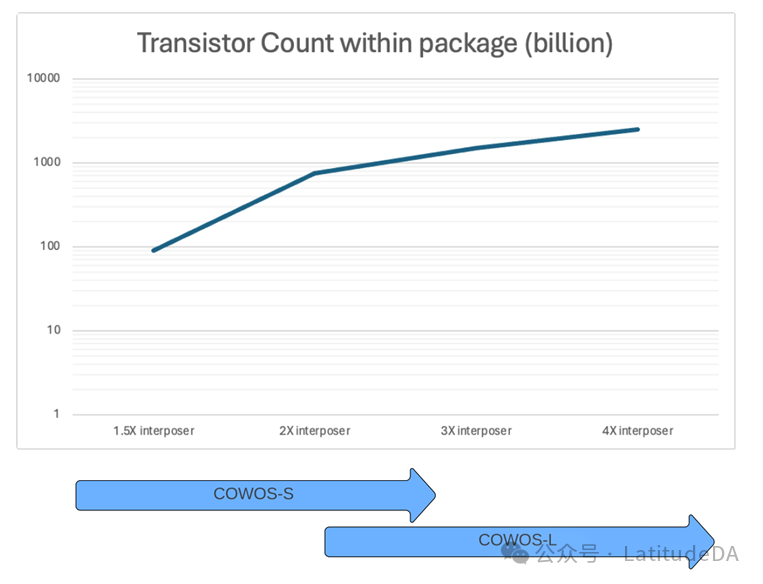

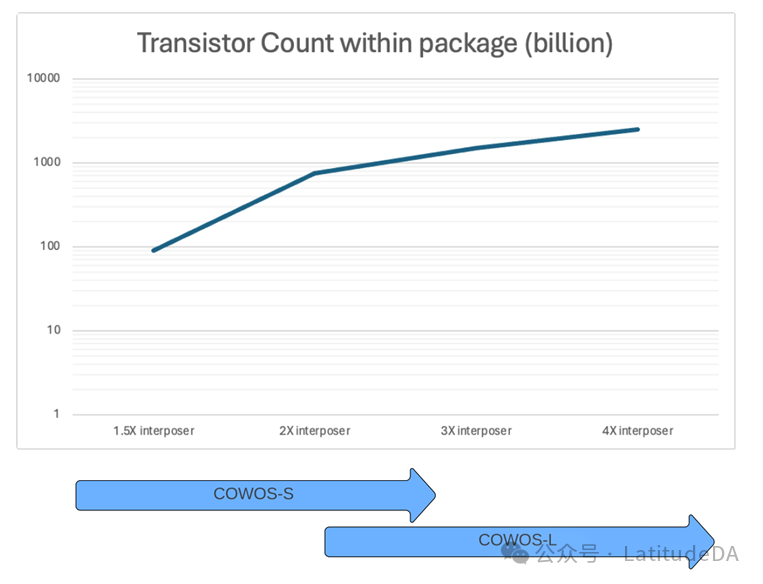

與系統(tǒng)級(jí)芯片 (SiP) 等老式封裝技術(shù)相比,CoWoS 技術(shù)可在封裝中支持更多晶體管。所有需要大量并行計(jì)算、處理大矢量數(shù)據(jù)和需要高內(nèi)存帶寬的應(yīng)用都最適合使用這種技術(shù)。

圖 4:隨著 CoWoS 的發(fā)展晶體管數(shù)量增加

許多公司都因 CoWoS 軟件包的成功而蓬勃發(fā)展。例如:

圖 4:隨著 CoWoS 的發(fā)展晶體管數(shù)量增加

許多公司都因 CoWoS 軟件包的成功而蓬勃發(fā)展。例如:

1.英偉達(dá)公司(NVIDIA)的人工智能芯片依賴(lài)于 CoWoS 軟件包。

2.AMD 也在探索將 CoWoS 封裝用于其人工智能芯片。

3.聯(lián)發(fā)科與臺(tái)積電合作,將 CoWoS 用于其網(wǎng)絡(luò) ASIC。

4.博通公司(Broadcom)將 CoWoS-L 用于其滿(mǎn)足深度學(xué)習(xí)和網(wǎng)絡(luò)應(yīng)用的 ASIC。

5.Global Unichip Corp. (GUC) 也與臺(tái)積電合作,將 CoWoS 用于其人工智能、高性能計(jì)算和網(wǎng)絡(luò)應(yīng)用芯片。

CoWoS 技術(shù)提供了更高的集成度,使集成電路能夠擴(kuò)展以滿(mǎn)足不斷增長(zhǎng)的計(jì)算能力需求。該技術(shù)正在不斷發(fā)展,以確保更高的良率、穩(wěn)健的電源和熱完整性,并進(jìn)一步增加插層面積,使更多晶圓能夠共享同一基板。未來(lái)幾年,CoWoS 將繼續(xù)推動(dòng)半導(dǎo)體行業(yè)的發(fā)展。

[1]https://anysilicon.com/cowos-package/

[2]“Test Challenges in Designing Complex 3D Chips: What in on the Horizon for EDA Industry”, by Sandeep K. Goyal.

[3]“Wafer Level System Integration of the Fifth Generation CoWoS?-S with High Performance Si Interposer at 2500 mm2”, by Huang et al.

[4]“CoWoS Architecture Evolution for Next Generation HPC on 2.5D System in Package”, by Hu et al.

- END -

免責(zé)聲明:本文采摘自網(wǎng)絡(luò),本文僅代表作者個(gè)人觀點(diǎn),不代表薩科微及行業(yè)觀點(diǎn),只為轉(zhuǎn)載與分享,支持保護(hù)知識(shí)產(chǎn)權(quán),轉(zhuǎn)載請(qǐng)注明原出處及作者,如有侵權(quán)請(qǐng)聯(lián)系我們刪除。

圖片來(lái)源: 臺(tái)積電

圖片來(lái)源: 臺(tái)積電

圖 1:CoWoS-S 封裝

圖 1:CoWoS-S 封裝

圖 2:CoWoS-R 封裝

圖 2:CoWoS-R 封裝

圖 3:CoWoS-L 封裝

圖 3:CoWoS-L 封裝

圖 4:隨著 CoWoS 的發(fā)展晶體管數(shù)量增加

圖 4:隨著 CoWoS 的發(fā)展晶體管數(shù)量增加