服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2022-10-25作者來源:薩科微瀏覽:7013

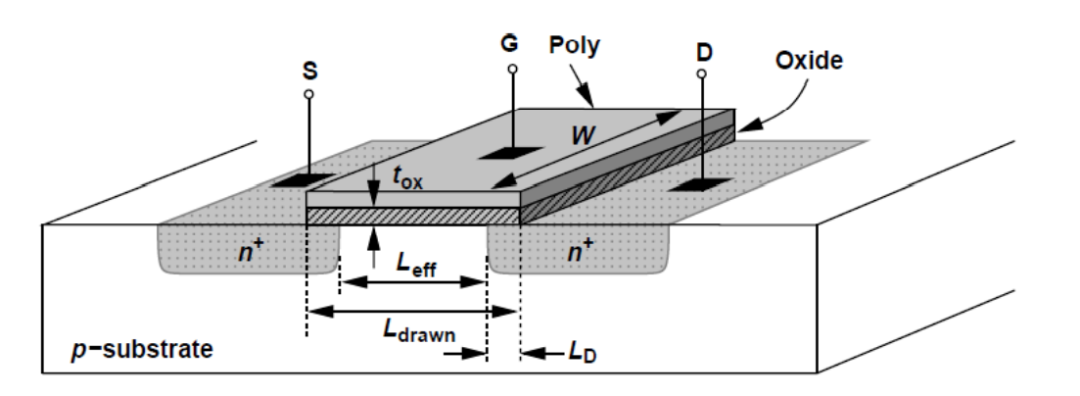

是多晶硅柵和襯底的功函數(shù)之差的電壓值,

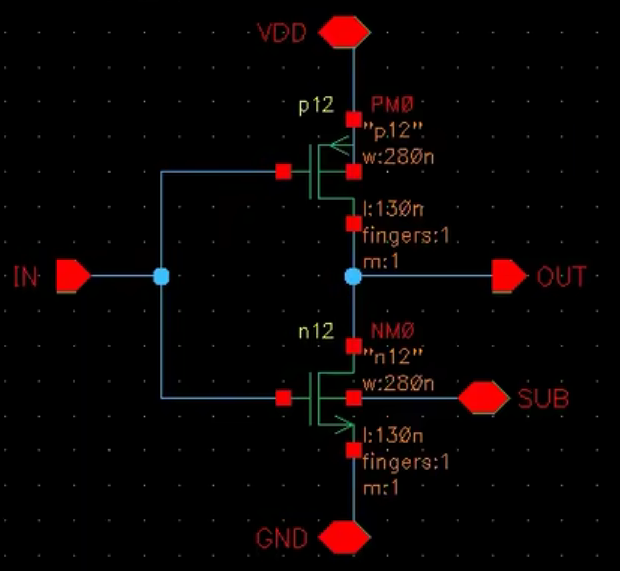

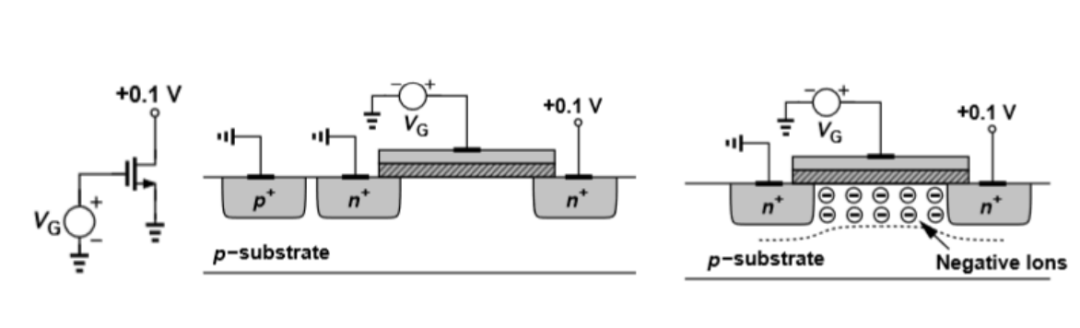

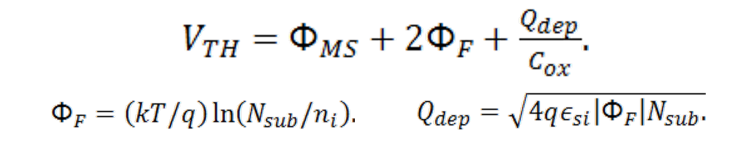

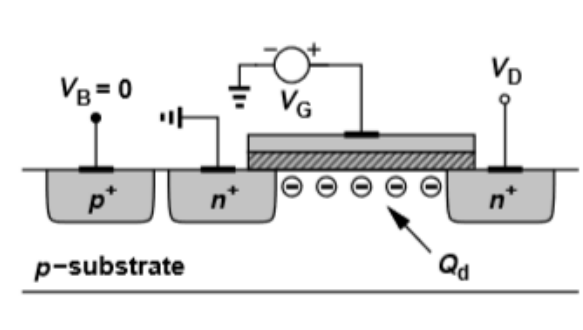

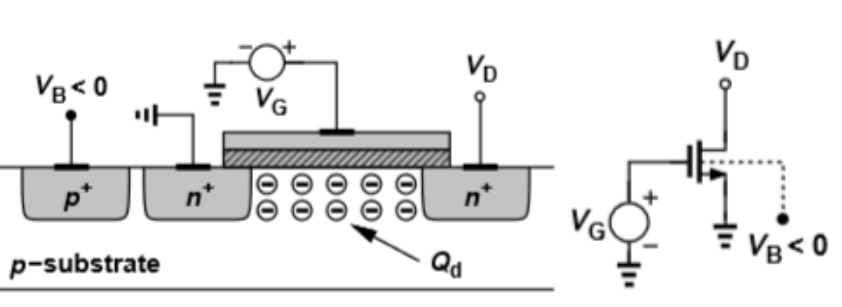

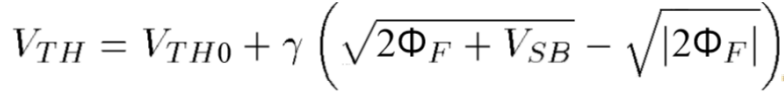

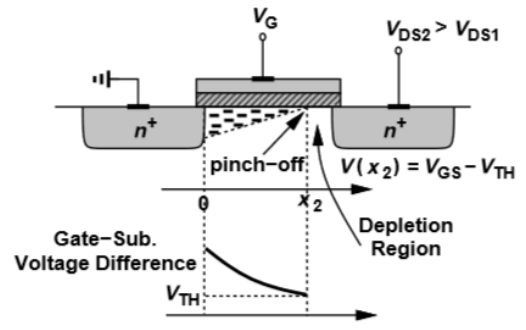

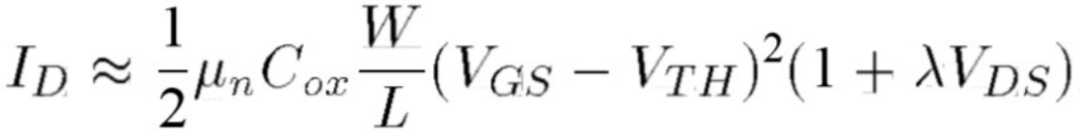

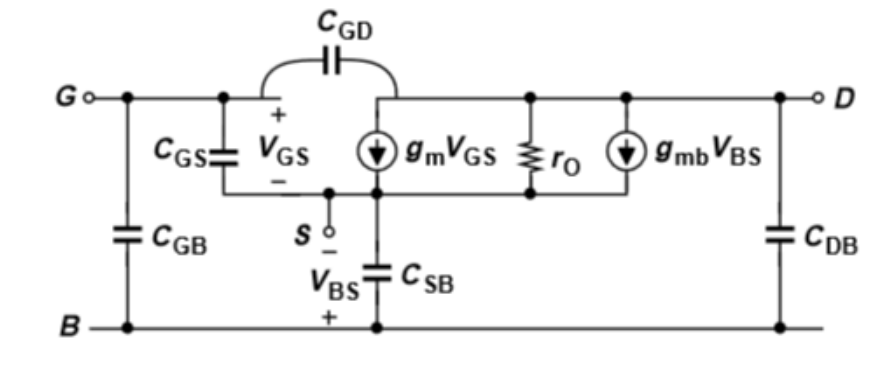

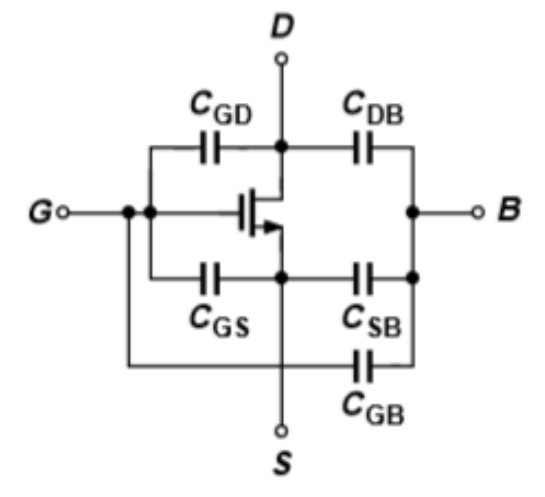

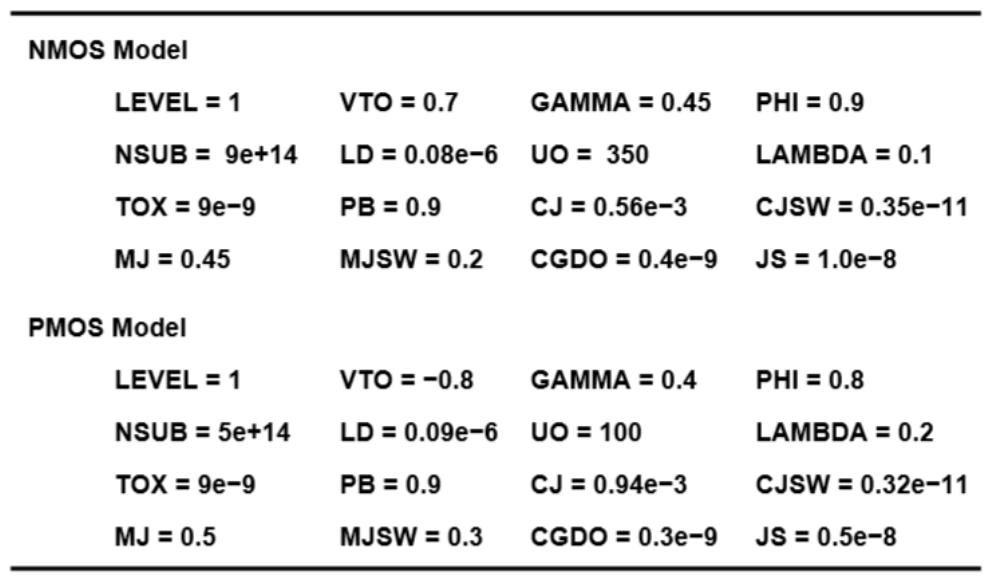

是多晶硅柵和襯底的功函數(shù)之差的電壓值, 里面的Nsub是襯底的摻雜濃度,q是電子電荷,ni是硅的本征載流子濃度,Qdep是耗盡區(qū)的電荷,Cox是單位面積的柵氧化層電容。

里面的Nsub是襯底的摻雜濃度,q是電子電荷,ni是硅的本征載流子濃度,Qdep是耗盡區(qū)的電荷,Cox是單位面積的柵氧化層電容。

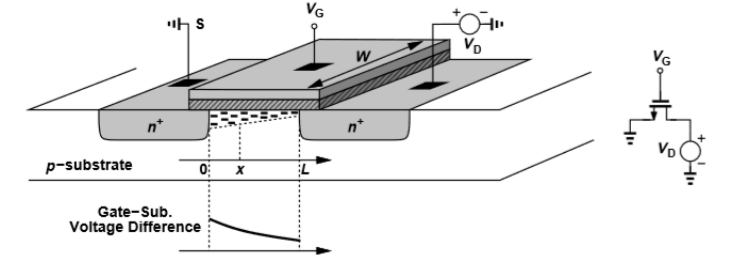

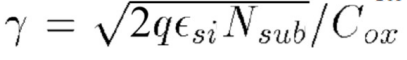

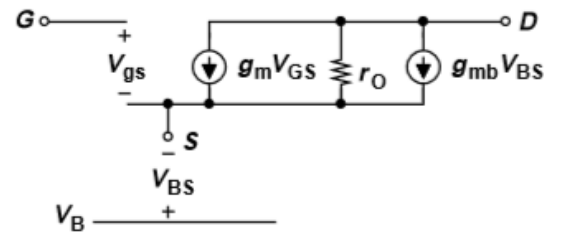

為體效應(yīng)系數(shù),同樣的,一般我們工藝廠家會(huì)在SPICE文件中給出這個(gè)值,在我們計(jì)算的時(shí)候直接帶進(jìn)去就可以的。

為體效應(yīng)系數(shù),同樣的,一般我們工藝廠家會(huì)在SPICE文件中給出這個(gè)值,在我們計(jì)算的時(shí)候直接帶進(jìn)去就可以的。

免責(zé)聲明:本文采摘自網(wǎng)絡(luò),僅代表作者個(gè)人觀點(diǎn),不代表薩科微及行業(yè)觀點(diǎn),只為轉(zhuǎn)載與分享,支持保護(hù)知識(shí)產(chǎn)權(quán),轉(zhuǎn)載請(qǐng)注明原出處及作者,如有侵權(quán)請(qǐng)聯(lián)系我們刪除。

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2024 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號(hào)-1