服務(wù)熱線

0755-83044319

發(fā)布時間:2022-12-08作者來源:薩科微瀏覽:1580

在晶體管發(fā)明 75 周年之際,我想回答兩個問題:世界需要更好的晶體管嗎?如果是這樣,他們會是什么樣子?

我會爭辯說,是的,我們將需要新的晶體管,而且我認為我們今天已經(jīng)有了一些關(guān)于它們會是什么樣子的暗示。問題在于我們是否有意愿和經(jīng)濟能力去制造它們。

我相信晶體管現(xiàn)在是并將繼續(xù)是應(yīng)對全球變暖影響的關(guān)鍵。氣候變化可能會給社會、經(jīng)濟和個人帶來巨變,因此需要能夠賦予我們?nèi)祟惛竽芰Φ墓ぞ摺?

半導(dǎo)體可以像其他技術(shù)一樣提高人類的能力。根據(jù)定義,所有技術(shù)都可以提高人類的能力。但對他們中的大多數(shù)人來說,自然資源和能源的限制使得數(shù)量級的改善值得懷疑。基于晶體管的技術(shù)是一個獨特的例外,原因如下:

|

1 |

隨著晶體管的改進,它們使新的能力成為可能,例如計算和高速通信、互聯(lián)網(wǎng)、智能手機、內(nèi)存和存儲、機器人技術(shù)、人工智能,以及其他還沒有人想到的東西。 |

|

2 |

這些能力具有廣泛的應(yīng)用,它們改變了所有技術(shù)、行業(yè)和科學(xué)。

半導(dǎo)體技術(shù)的增長不像其他技術(shù)那樣受到其材料和能源使用的限制。IC 使用相對少量的材料。因此,它們變得越來越小,它們使用的材料越少,它們變得越快、越節(jié)能、越有能力。 |

|

3 |

從理論上講,信息處理所需的能量仍然可以減少到今天所需能量的千分之一以下。雖然我們還不知道如何達到這種理論效率,但我們知道將能源效率提高一千倍并不違反物理定律。相比之下,大多數(shù)其他技術(shù)(例如電機和照明)的能源效率已經(jīng)達到其理論極限的 30% 到 80%。

|

晶體管:過去、現(xiàn)在和未來

我們將如何繼續(xù)改進晶體管技術(shù)在短期內(nèi)是相對清楚的,但離今天越遠,它就會變得越模糊。在短期內(nèi),您可以通過查看最近的過去來瞥見晶體管的未來。

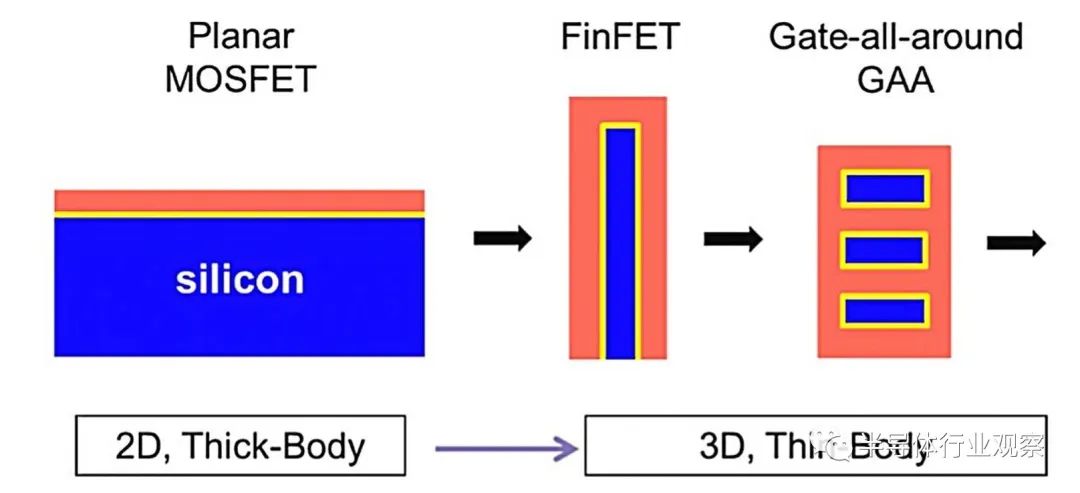

從 1960 年到 2010 年左右,基本的平面 (2D) MOSFET 結(jié)構(gòu)一直保持不變,直到進一步增加晶體管密度和降低器件功耗變得不可能。我(代表本文作者胡正明)在加州大學(xué)伯克利分校的實驗室早在十多年前就看到了這一點。我們在 1999 年報道了平面晶體管的后繼者 FinFET 的發(fā)明。FinFET 作為[敏感詞]個 3D MOSFET,將扁平而寬的晶體管結(jié)構(gòu)變?yōu)楦叨木w管結(jié)構(gòu)。好處是在更小的占地面積內(nèi)獲得更好的性能,就像在擁擠的城市中多層建筑相對于單層建筑的優(yōu)勢一樣。

FinFET 也就是所謂的薄體(thin-body)MOSFET,這一概念繼續(xù)指導(dǎo)新設(shè)備的開發(fā)。它源于這樣一種認識,即電流不會通過硅表面幾納米內(nèi)的晶體管泄漏,因為那里的表面電勢受到柵極電壓的良好控制。FinFET 牢記這種薄體概念。該器件的主體是垂直的硅鰭片,被氧化物絕緣體和柵極金屬覆蓋,在強柵極控制范圍之外沒有留下任何硅。FinFET 將漏電流降低了幾個數(shù)量級,并降低了晶體管工作電壓。它還指出了進一步改進的路徑:進一步降低車身厚度。

FinFET 的鰭片隨著每個新的技術(shù)節(jié)點變得越來越薄和越來越高。但這種進步現(xiàn)在變得難以維持。因此業(yè)界正在采用一種新的 3D 薄體 CMOS 結(jié)構(gòu),稱為環(huán)柵 (GAA)。在這種新結(jié)構(gòu)上,一堆半導(dǎo)體帶構(gòu)成了薄體(a stack of ribbons of semiconductor make up the thin body)。

MOSFET 結(jié)構(gòu)的每一次演變都旨在通過柵極 [粉紅色] 更好地控制硅中的電荷。電介質(zhì) [[敏感詞]] 防止電荷從柵極移動到硅體 [藍色]。

3D 薄體趨勢將從這些 3D 晶體管延續(xù)到 3D 堆疊晶體管、3D 單芯片(Monolithic)電路和多芯片封裝。在某些情況下,這種 3D 趨勢已經(jīng)達到了[敏感詞]。例如,電荷陷阱(charge-trap)存儲器晶體管陣列的規(guī)律性使 NAND 閃存成為[敏感詞]個從 2D 電路過渡到 3D 電路的 IC。自 2007 年東芝首次報告 3D NAND 以來,堆疊層數(shù)已從 4 層增長到超過 200層。

單芯片 3D 邏輯 IC 可能會適度起步,堆疊 CMOS 反相器的兩個晶體管以減少所有邏輯門的“占地面積”。但是堆棧的數(shù)量可能會增加。通往 3D IC 的其他途徑可能采用將額外的半導(dǎo)體薄膜層(例如硅、硅鍺或砷化銦鎵)轉(zhuǎn)移或沉積到硅晶片上。

薄體趨勢可能會在二維半導(dǎo)體中達到其最終終點,其厚度以原子為單位。例如,二硫化鉬分子(Molybdenum disulfide molecules)既天然又薄又相對較大,形成可能不超過三個原子寬但具有非常好的半導(dǎo)體特性的二維半導(dǎo)體。2016 年,加利福尼亞州和德克薩斯州的工程師使用二維半導(dǎo)體分子二硫化鉬和碳納米管薄膜展示了具有關(guān)鍵尺寸的 MOSFET:柵極長度僅為 1 納米。即使柵極短至 1 nm,晶體管漏電流也僅為每毫米 10 毫微安,可與當(dāng)今[敏感詞]的生產(chǎn)晶體管相媲美。

可以想象,在遙遠的未來,整個晶體管可能被預(yù)制為一個分子(molecule)。這些預(yù)制構(gòu)件可能會通過稱為定向自組裝 (DSA:directed-self-assembly) 的制程被帶到它們在 IC 中的精確位置。要理解 DSA,回顧一下 COVID 病毒使用其尖峰來尋找并化學(xué)停靠在特定人類細胞表面的確切位置可能會有所幫助。在 DSA 中,對接點(docking spots)、“尖峰”(spikes)和晶體管cargo都是經(jīng)過精心設(shè)計和制造的。最初的對接點(docking spots)可以通過在基板上進行光刻來創(chuàng)建,但是額外的對接點(docking spots)可能會在后續(xù)步驟中作為 cargo 引入。如果僅在制造過程中需要而在最終產(chǎn)品中不需要,則可以通過加熱或其他方式去除一些 cargo 。

除了使晶體管更小之外,我們還必須不斷降低它們的功耗。在這里,我們可以看到通過使用所謂的負電容場效應(yīng)晶體管 (NCFET:negative-capacitance field-effect transistors) 實現(xiàn)了數(shù)量級的減少。這些需要在 MOSFET 的柵極堆疊中[敏感詞]納米薄的鐵電材料層,例如氧化鉿鋯(hafnium zirconium oxide)。由于鐵電體包含自己的內(nèi)部電場,因此打開或關(guān)閉設(shè)備所需的能量更少。薄鐵電體的另一個優(yōu)點是可以利用鐵電體的容量來存儲其電場狀態(tài),從而將存儲和計算集成在同一設(shè)備中。

作者 [左] 于 2016 年獲得巴拉克奧巴馬總統(tǒng) [右] 頒發(fā)的美國國家技術(shù)與創(chuàng)新獎?wù)?/span>

在某種程度上,我所描述的設(shè)備是從現(xiàn)有趨勢中產(chǎn)生的。但未來的晶體管可能與今天的晶體管具有截然不同的材料、結(jié)構(gòu)和工作機制。例如,納米機電開關(guān)(nanoelectromechanical switch)是對過去幾十年機械繼電器的回歸,而不是晶體管的延伸。它不依賴于半導(dǎo)體物理學(xué),而是僅使用金屬、電介質(zhì)以及施加不同電壓的緊密間隔的導(dǎo)體之間的力。

所有這些例子都在幾年前用實驗證明了。然而,與以往的半導(dǎo)體技術(shù)突破相比,將它們投入生產(chǎn)需要更多的時間和精力。

走向未來

我們能否實現(xiàn)這些壯舉?過去的一些教訓(xùn)表明我們可以。

[敏感詞]個教訓(xùn)是晶體管技術(shù)的進步并不平坦或順利。1980 年前后,每顆芯片的功耗上升到了令人痛苦的地步。采用 CMOS、取代 NMOS 和雙極技術(shù)后——工作電壓從 5 伏逐漸降低到 1 伏——為該行業(yè)帶來了 30 年或多或少的直截了當(dāng)?shù)倪M步。但是,功耗再次成為一個問題。2000 年至 2010 年間,有思想的研究人員預(yù)測每平方厘米 IC 產(chǎn)生的熱量很快就會達到核反應(yīng)堆堆芯的熱量。3D薄體FinFET和多核處理器架構(gòu)的采用避免了危機,迎來了又一個相對平穩(wěn)的發(fā)展時期。

晶體管技術(shù)的發(fā)展史可謂一座座山峰攀登。只有當(dāng)我們到達一座山頂時,我們才能看到遠處的景色,并繪制出一條路線來攀登下一座更高更陡的山峰。

第二個教訓(xùn)是,半導(dǎo)體產(chǎn)業(yè)的核心力量——納米加工——非常強大。歷史證明,只要有足夠的時間和經(jīng)濟激勵,只要該想法不違反科學(xué)規(guī)律,該行業(yè)就能夠?qū)⑷魏蜗敕ㄗ優(yōu)楝F(xiàn)實。

但該行業(yè)是否有足夠的時間和經(jīng)濟激勵來繼續(xù)攀登更高更陡峭的山峰并不斷提高人類的能力?

這是一個公平的問題。隨著晶圓廠行業(yè)資源的增長,技術(shù)發(fā)展的山峰增長得更快。終有一天,沒有一家晶圓廠公司能夠登上山頂,看清前方的道路。那么會發(fā)生什么?

所有半導(dǎo)體晶圓廠(包括獨立的和像英特爾這樣的綜合性公司)的收入約占半導(dǎo)體行業(yè)收入的三分之一。但晶圓廠僅占半導(dǎo)體技術(shù)所帶來的 IT、電信和消費電子行業(yè)總收入的 2%。然而,晶圓廠行業(yè)承擔(dān)著發(fā)現(xiàn)、生產(chǎn)和營銷新晶體管和納米制造技術(shù)的大部分重擔(dān),這需要改變了。

為了讓該行業(yè)生存,晶圓廠行業(yè)相對貧乏的資源必須優(yōu)先考慮晶圓廠建設(shè)和股東需求,而不是科學(xué)探索。雖然晶圓廠行業(yè)正在延長其研究時間范圍,但它也需要其他人來承擔(dān)責(zé)任。人類長期解決問題的能力值得有針對性的公眾支持。該行業(yè)需要長期探索性研究的幫助,公共資助,在類似貝爾實驗室的環(huán)境中,或者由大學(xué)研究人員提供,這些研究人員具有長期的職業(yè)生涯,并且在物理、化學(xué)、生物學(xué)和算法方面的知識比企業(yè)研究更廣泛和更深入目前允許。

這樣,人類將繼續(xù)尋找新的晶體管,并獲得應(yīng)對未來幾個世紀(jì)挑戰(zhàn)所需的能力。

友情鏈接:站點地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2024 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號-1