服務熱線

0755-83044319

發布時間:2022-05-28作者來源:薩科微瀏覽:2512

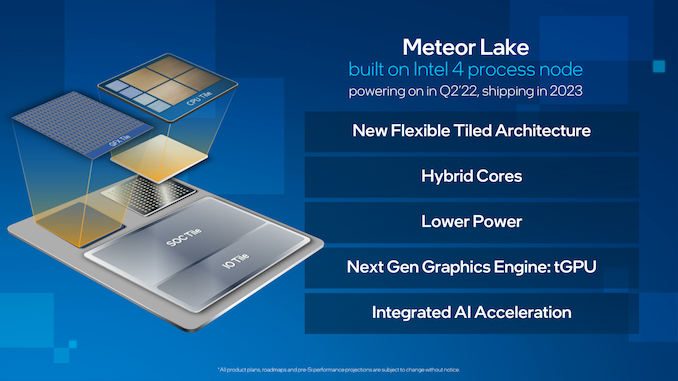

Intel: Meteor Lake Chiplet SoC Up and Running

說到芯片領域的動態,最近一個月內,先是英特爾在4月宣布其[敏感詞]款采用Chiplet設計的大眾SoC“Meteor Lake” 完成通電測試。不過一個月以后,AMD公布其正在計劃加快CPU及GPU規格迭代,將全面導入Chiplet設計,以提高核心數量及運算速度,此外,其新一代5nm Zen 4架構將采用Chiplet設計。這一波超異構、Chiplet浪潮的掀起,不僅將對英特爾和AMD產生深遠的影響,還沖擊了整個半導體行業。

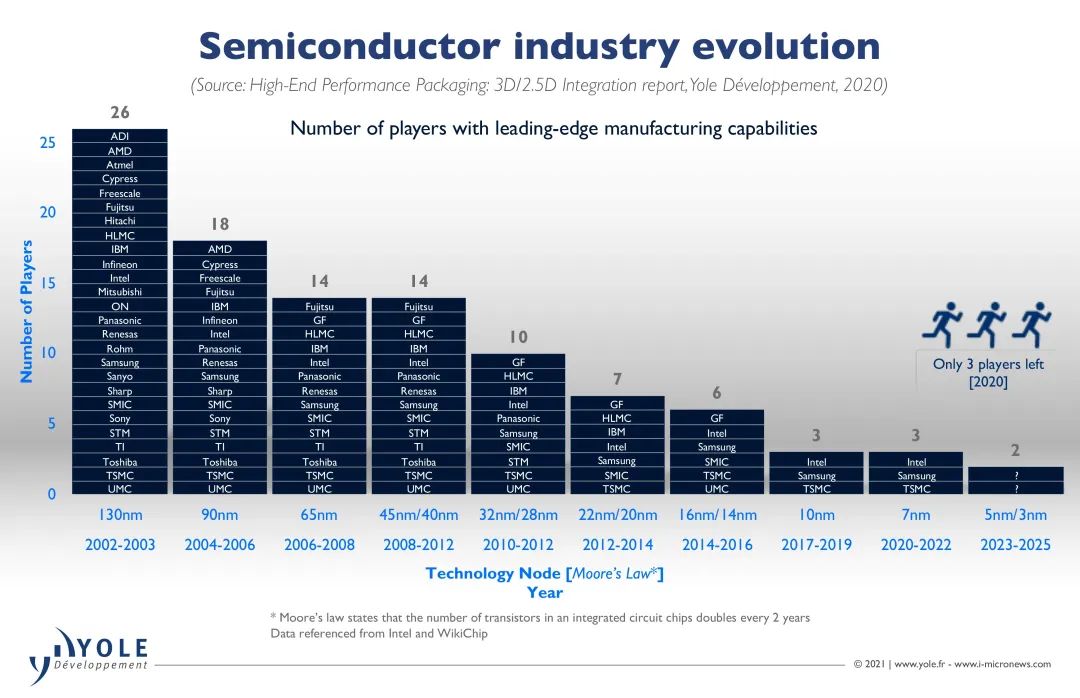

01先進制程:諸神之戰,凡人莫及

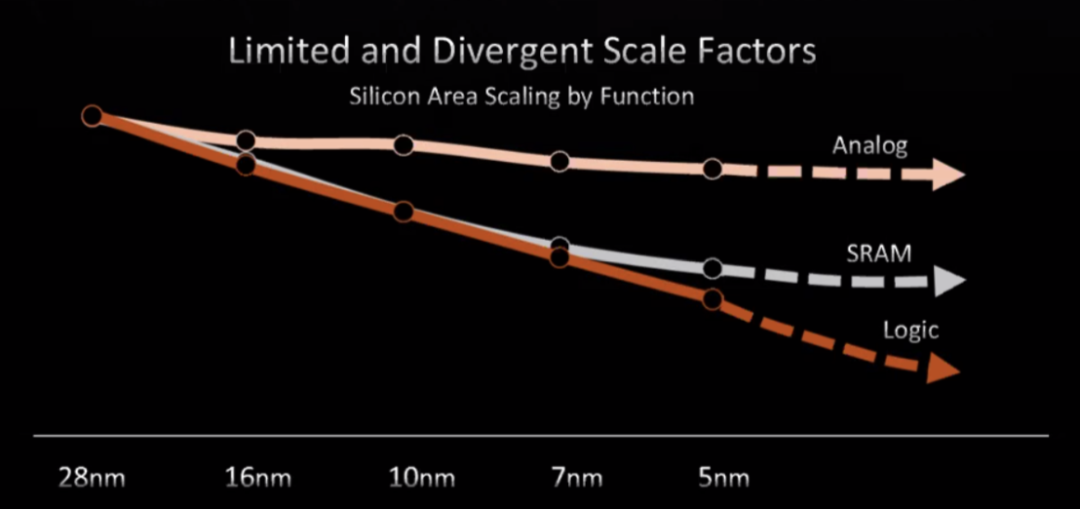

芯片苦于制程久矣。近日,臺積電宣布開發1.4納米工藝,晶體管尺寸逼近字面意義上的物理極限。不斷燒錢死磕制程的路線難以為繼,已成了行業公認的事實,原因有三:[敏感詞],性能極限:通過先進制程微縮對芯片性能的提升覆蓋面有限;第二,技術極限:納米級的晶體管集成度和精細化程度非常高,引發了短溝道效應和量子隧穿難題;當然,還有最核心成本極限:

--半導體行業分析師Douglas O’laughlin

Chiplet Meets The Real World -- Benefits and Limits of Chiplet Designs ” (Source:AMD)

FinFET時代玩家僅剩英特爾、臺積電、三星(Source: Yole Développement)

02制程越小,性能真的越高?

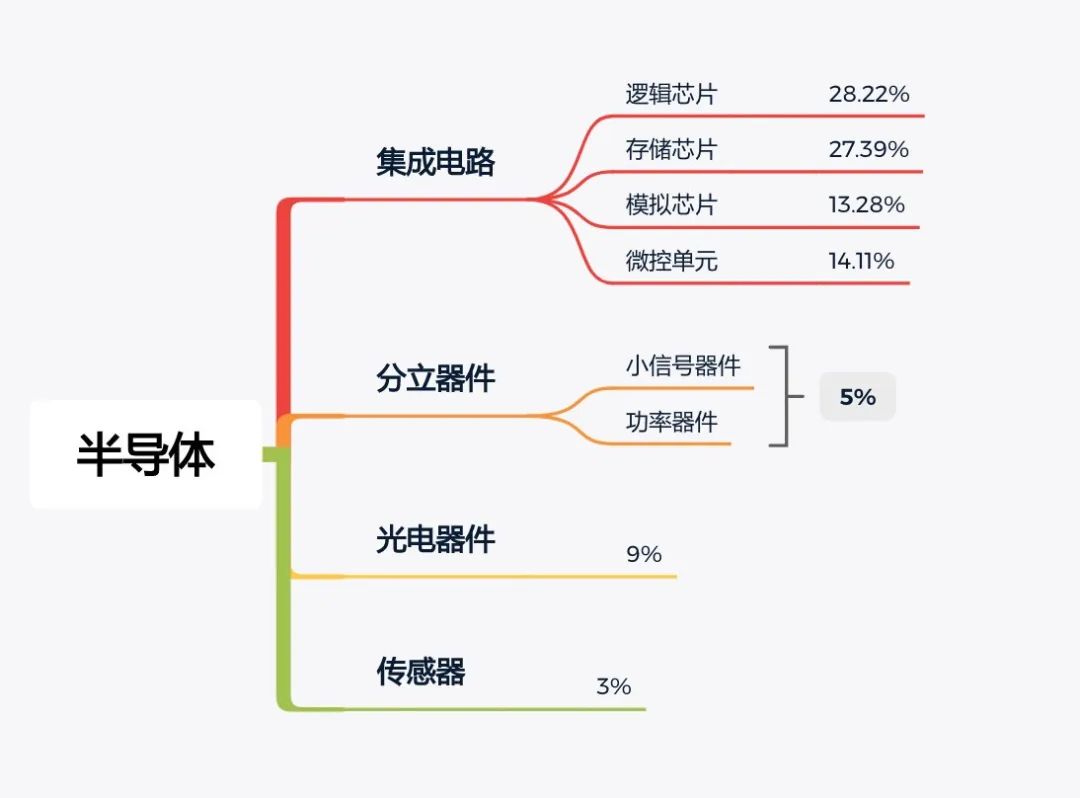

邏輯芯片:人類芯片科技的皇冠,制作工藝復雜,如CPU、GPU、AI、MCU。受益于先進制程技術的進步,邏輯芯片依然沿著摩爾定律向前演進,現在已經5nm產線已經量產,3nm已排上日程。

存儲芯片:與邏輯芯片相比,內部結構相對簡單,主要分為DRAM、NAND Flash、NORFlash三類。以DRAM為例,當制程到了18/16nm以下,繼續縮減尺寸已不再具備成本和性能方面的優勢。

Limited and Divergent Scale Factors(Source: AMD)

03超異構計算,何以為“超”

要了解超異構,首先要理解什么是異構。從字面意思來看,異構就是同構的反義詞,即“不同的架構或者結構”。用核酸測試舉例,十個大白同去一個街道給居民們測核酸,計劃每人負責十分之一的居民,這就是同構。但是在執行過程中,大白發現,居民們的情況不同,有些樓棟有陽性患者,需要上門檢測;有些居民不積極,需要多次催促;有些居民腿腳不便,需要專人攙扶;此外,還有核酸碼掃描、登記,發放抗原試劑等工作。于是,大白們根據實際需求重新劃分了工作職責,進行人員的安排和工作的優先級劃分,如陽性樓棟最后采樣,從而[敏感詞]限度地提高工作效率,這就是異構。

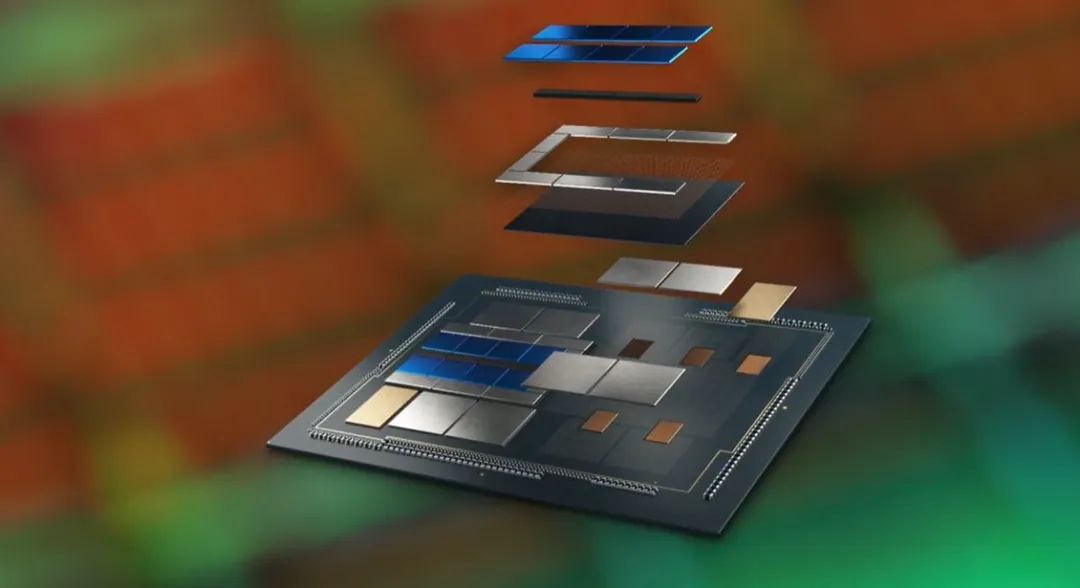

而“超異構計算”,則在于超過了異構計算的瓶頸,它可以把很多現有的、不同節點上已經驗證過的晶片集成在一個封裝里(經過協調,大白和來自其他地區的民警、居委會人員、甚至外省支援的人員,共同應對情況復雜的街道)。超異構計算在傳統的異構計算基礎上,通過更強大的模塊化Chiplet能力,封裝互連能力和軟件能力,將越來越復雜的系統整合成了宏系統芯片MSOC(Macro-System on Chip)。

如今,基于超異構計算的架構創新正在成為芯片巨頭們的未來驅動力。通過一連串的收購和自研行為,全球三大處理器頭部廠商都在向CPU+GPU+FPGA/NPU的方向靠攏,構建超異構計算體系。

NVIDIA擬收購 Arm,其目的在于增強其服務器CPU能力,雖然最終未能收購成功,NVIDIA仍獲得了未來10年Arm開發授權。

AMD對賽靈思的收購,也釋放出強化異構計算布局的信號,成功彌補了FPGA短板。同時,賽靈思在異構計算上也有所積累,已推出Versal ACAP異構計算平臺,以縮短車載多傳感器同步和融合所帶來的系統整體響應時間。冥冥之中,超異構計算時代已起飛。

03Chiplet,超異構未來驅動力

在“超異構”的三大核心能力中,被通俗地解釋為 “樂高積木” 的Chiplet技術,被視為“超異構”的關鍵驅動力。這正是AMD在新一代5nm Zen 4架構中采用,并與臺積電聯合研發的用于CPU封裝的技術。與傳統芯片設計方式相比,Chiplet具有迭代周期快,成本低,良率高等一系列優勢:

Intel Ponte Vecchio Suspended

1

降低芯片成本

SoC設計的一大難題是,不同的模塊對制程的敏感度不同,如模擬電路、大功率 I/Os 、射頻等對制程不敏感,沒有使用高端制程的必要。所以,如果可以將像搭積木一樣制造芯片,針對功能選擇合適的制程,不但能讓芯片尺寸變得更小,還可以提高良率,降低制造成本,實現性能[敏感詞]化;此外,基于 Chiplet 設計的SoC 還可對外采購具備特定功能的裸片,以節省自身的開發和驗證成本。

2

縮減芯片開發周期

與從0開始開發一款 SoC 相比,Chiplet 能大幅縮減芯片開發周期,幫助芯片公司盡快推出產品,贏得競爭優勢和市場份額。

3

提升設計靈活性

通過3D高密度互聯技術,對連接到底層邏輯芯片的模塊芯片在原則上沒有限制。廠商可以根據模塊的特點,選擇性價比[敏感詞]的工藝節點進行制造,提升芯片設計的靈活性。同時,通過3D高密度集成,Chiplet 能幫助增加芯片核心單元面積,提高單芯片算力。

4

拓寬下游市場

由于目前的芯片下游市場高度細分,很多細分市場的終端出貨量不足以支撐 SoC 高昂的 Mask 成本,芯片設計公司只會針對下游出貨量較大(如智能手機)或利潤較高的市場。而基于 Chiplet 的設計,可以讓芯片設計公司針對規模適中的市場(智能汽車/服務器等)以較低的成本開發出高性能的解決方案,擴寬了下游市場。

04Chiple行業生態

今年3月,全球芯片頭部制造企業Intel、AMD、ARM、Google Cloud、Meta、Microsoft、Qualcomm、Samsung、TSMC等聯合宣布成立Chiplet聯盟,并推出了一個全新的通用芯片互連標準(UCle),該組織發布了一種新的開放式芯片間互連規范,使芯粒能夠在封裝中相互通信。借助UCIe平臺,巨頭們將打造更加完整的Chiplet生態系統,并呼吁更多半導體企業的加入。

免責聲明:本文采摘自網絡,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1