服務熱線

0755-83044319

發布時間:2022-03-10作者來源:薩科微瀏覽:2446

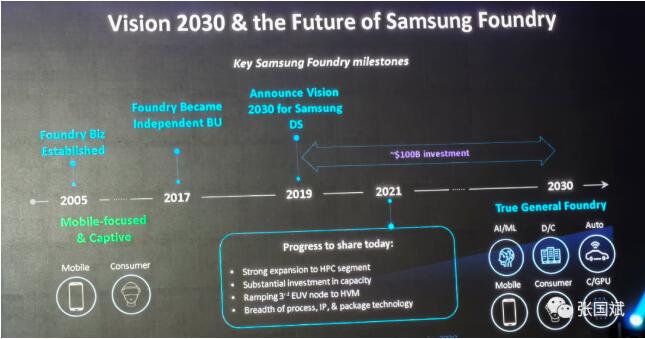

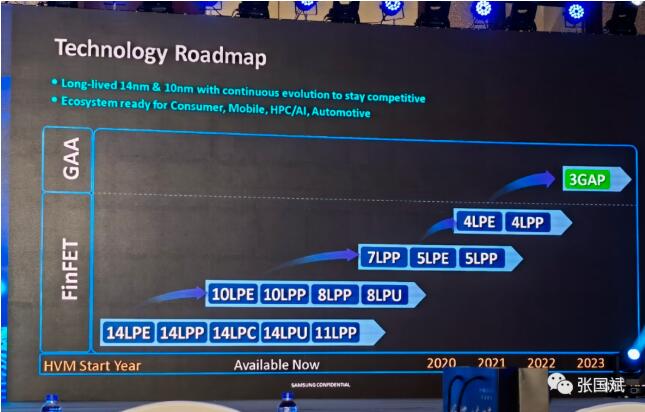

YK Lee的PPT顯示,三星將在2023年量產3nm GAA工藝技術。

YK Lee的PPT顯示,三星將在2023年量產3nm GAA工藝技術。

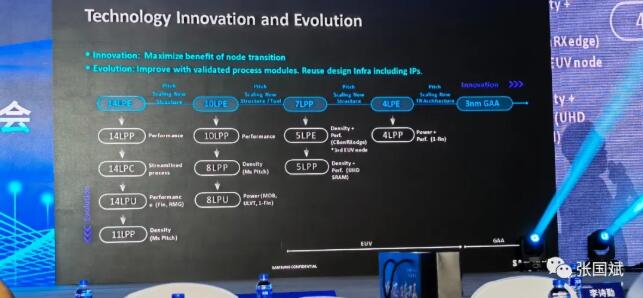

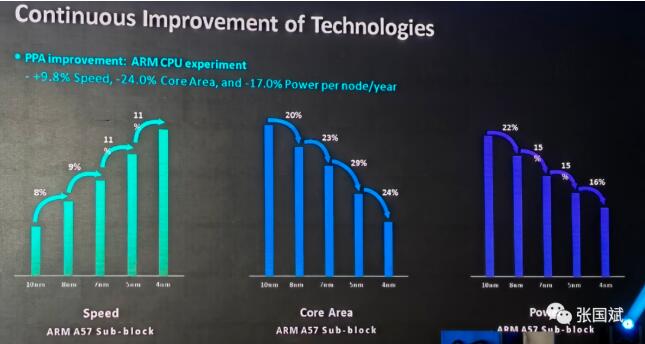

他表示在每一代工藝上,三星都有改進

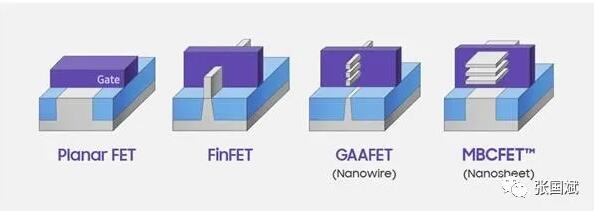

幾天前,三星宣布3nm GAA流片成功。在3nm節點,三星選擇了下一代工藝技術——GAA環繞柵極晶體管,通過使用納米片設備制造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代FinFET晶體管技術。

幾天前,三星宣布3nm GAA流片成功。在3nm節點,三星選擇了下一代工藝技術——GAA環繞柵極晶體管,通過使用納米片設備制造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),該技術可以顯著增強晶體管性能,主要取代FinFET晶體管技術。

根據三星的說法,與5nm制造工藝相比,3nm GAA技術的邏輯面積效率提高了35%以上,功耗降低了50%,性能提高了約30%。

根據三星的說法,與5nm制造工藝相比,3nm GAA技術的邏輯面積效率提高了35%以上,功耗降低了50%,性能提高了約30%。 三星早在2019年就公布了3nm GAA工藝的PDK物理設計套件標準,這次3nm芯片流片是跟Synopsys合作完成的,雙方聯合驗證了該工藝的設計、生產流程,是3nm GAA工藝的里程碑。

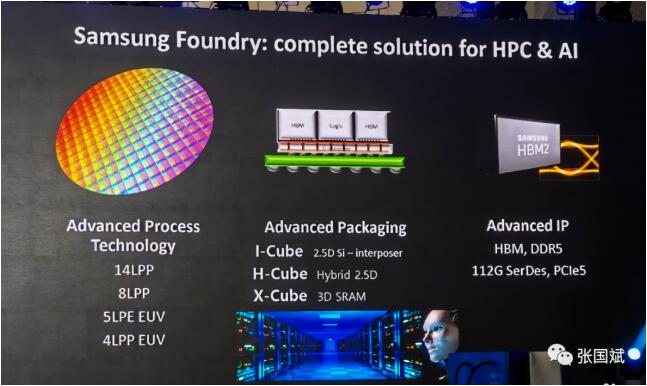

三星早在2019年就公布了3nm GAA工藝的PDK物理設計套件標準,這次3nm芯片流片是跟Synopsys合作完成的,雙方聯合驗證了該工藝的設計、生產流程,是3nm GAA工藝的里程碑。 針對AI和高性能計算,三星有完整的解決方案,分別是高級工藝、高級封裝和高級ip。

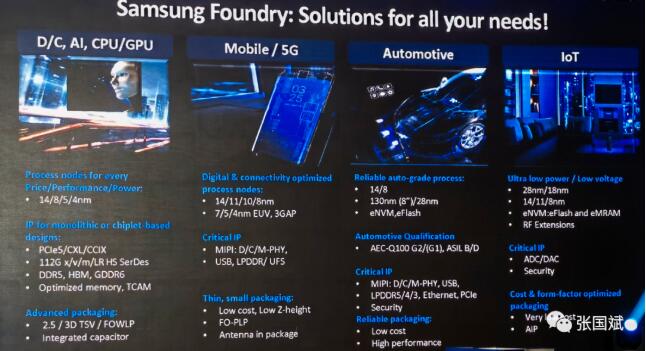

針對AI和高性能計算,三星有完整的解決方案,分別是高級工藝、高級封裝和高級ip。

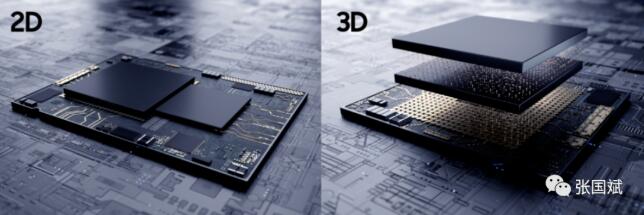

在高級封裝上,半導體領頭羊都有自己的技術,臺積電有CoWoS,Intel有Foveros。三星的3D封裝技術叫X-Cube。

在高級封裝上,半導體領頭羊都有自己的技術,臺積電有CoWoS,Intel有Foveros。三星的3D封裝技術叫X-Cube。

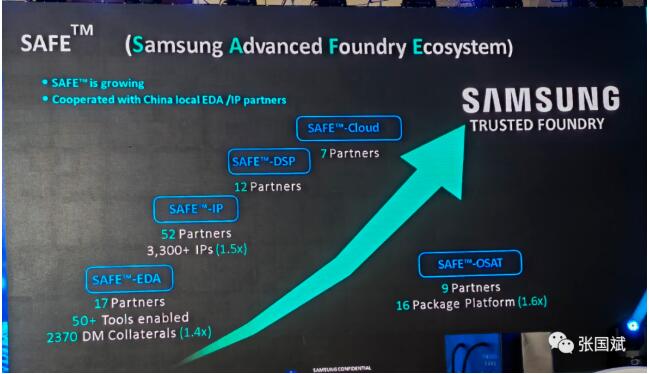

X-Cube的全稱是eXtended-Cube,意為拓展的立方體。在Die之間的互聯上面,它使用的是成熟的TSV工藝,即硅穿孔工藝。目前三星自己的X-Cube測試芯片已經能夠做到將SRAM層堆疊在邏輯層之上,通過TSV進行互聯,制程是他們自家的7nm EUV工藝。三星表示這樣可以將SRAM與邏輯部分分離,更易于擴展SRAM的容量。另外,3D封裝縮短了Die之間的信號距離,能夠提升數據傳輸速度并提高能效。 X-Cube可靈活應用于未來芯片之上,包括5G、AI和高性能計算等領域的芯片均可使用該技術。三星表示X-Cube已經在自家的7nm和5nm制程上面通過了驗證,計劃和無晶圓廠的芯片設計公司繼續合作,推進3D封裝工藝在下一代高性能應用中的部署。這個短視頻介紹了這個技術。 三星也有自己的高級代工生態計劃(SAFE)如在SAFE EDA領域,三星有12個合作伙伴,在SAFE IP 領域,三星有52個合作伙伴。

X-Cube的全稱是eXtended-Cube,意為拓展的立方體。在Die之間的互聯上面,它使用的是成熟的TSV工藝,即硅穿孔工藝。目前三星自己的X-Cube測試芯片已經能夠做到將SRAM層堆疊在邏輯層之上,通過TSV進行互聯,制程是他們自家的7nm EUV工藝。三星表示這樣可以將SRAM與邏輯部分分離,更易于擴展SRAM的容量。另外,3D封裝縮短了Die之間的信號距離,能夠提升數據傳輸速度并提高能效。 X-Cube可靈活應用于未來芯片之上,包括5G、AI和高性能計算等領域的芯片均可使用該技術。三星表示X-Cube已經在自家的7nm和5nm制程上面通過了驗證,計劃和無晶圓廠的芯片設計公司繼續合作,推進3D封裝工藝在下一代高性能應用中的部署。這個短視頻介紹了這個技術。 三星也有自己的高級代工生態計劃(SAFE)如在SAFE EDA領域,三星有12個合作伙伴,在SAFE IP 領域,三星有52個合作伙伴。

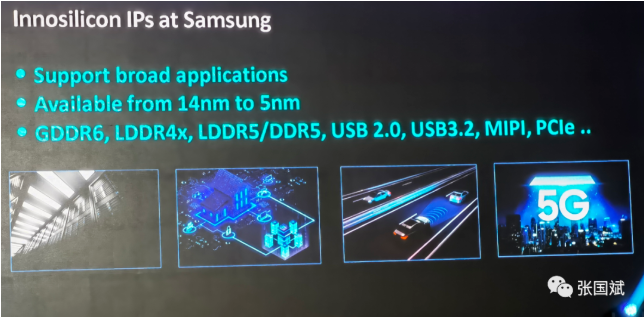

芯動科技就是三星的IP合作伙伴,主要在GDDR6,LPDDR4X等存儲器和接口方面合作。

芯動科技就是三星的IP合作伙伴,主要在GDDR6,LPDDR4X等存儲器和接口方面合作。

他表示三星會加大EUV產線,5月21日,三星宣布計劃提高其在韓國平澤市新生產線的晶圓代工生產能力。三星電子指出,該生產線已于本月開始建設,將專注于基于EUV的5納米及以下工藝技術,預計將于2021年下半年全面投入生產。

他表示三星會加大EUV產線,5月21日,三星宣布計劃提高其在韓國平澤市新生產線的晶圓代工生產能力。三星電子指出,該生產線已于本月開始建設,將專注于基于EUV的5納米及以下工藝技術,預計將于2021年下半年全面投入生產。

根據規劃,三星將于今年下半年開始在華城工廠開始批量生產5nm EUV工藝。加上平澤工廠,三星將在韓國和美國總共擁有7條晶圓代工生產線,其中包括6條12英寸生產線和1條8英寸生產線。 與7nm EUV工藝對比,三星5nm EUV工藝的性能提升10%,功耗降低了20%,邏輯面積效率提升25%。 總之,未來三星將是臺積電強勁對手,目前在美國和韓國,三星都有高端300mm晶圓廠。

根據規劃,三星將于今年下半年開始在華城工廠開始批量生產5nm EUV工藝。加上平澤工廠,三星將在韓國和美國總共擁有7條晶圓代工生產線,其中包括6條12英寸生產線和1條8英寸生產線。 與7nm EUV工藝對比,三星5nm EUV工藝的性能提升10%,功耗降低了20%,邏輯面積效率提升25%。 總之,未來三星將是臺積電強勁對手,目前在美國和韓國,三星都有高端300mm晶圓廠。

免責聲明:本文轉載自“電子創新網張國斌”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:202974035 陳經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2024 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1